Wafer

Als Wafer [] (englisch für „dünner Keks“ oder „dünne Brotscheibe“)[1][2] werden in der Mikroelektronik, Photovoltaik und Mikrosystemtechnik kreisrunde oder quadratische, etwa ein Millimeter dicke Scheiben bezeichnet. Sie werden aus ein- oder polykristallinen (Halbleiter-)Rohlingen, sogenannten Ingots, hergestellt und dienen in der Regel als Substrat (Grundplatte) für elektronische Bauelemente, unter anderem für integrierte Schaltkreise (IC, „Chip“), mikromechanische Bauelemente oder photoelektrische Beschichtungen. Bei der Fertigung von mikroelektronischen Bauelementen werden in der Regel mehrere Wafer zu einem Los zusammengefasst und direkt hintereinander oder auch parallel bearbeitet (vgl. Losfertigung).

Aufbau

Eine Scheibe besteht in den meisten Fällen aus monokristallinem Silicium, es werden aber auch andere Materialien wie Siliciumcarbid, Galliumarsenid und Indiumphosphid verwendet. In der Mikrosystemtechnik werden auch Glas-Wafer mit einer Dicke im 1-mm-Bereich verwendet.

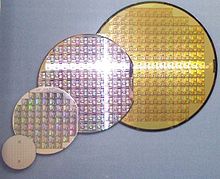

Die Scheiben werden in verschiedenen Durchmessern gefertigt. Die zurzeit hauptsächlich verwendeten Wafer-Durchmesser unterscheiden sich je nach Halbleiterwerkstoff und vorgesehenem Verwendungszweck (Silicium: 150 mm, 200 mm und 300 mm – 450 mm sind in der Diskussion; Gallium-Arsenid: 2 Zoll, 3 Zoll, 100 mm, 125 mm und 150 mm – 200 mm technisch machbar). Je größer der Wafer, desto mehr ICs können darauf untergebracht werden. Da bei größeren Wafern der geometrische Verschnitt kleiner wird, können die ICs kostengünstiger produziert werden (siehe Ausbeute (Halbleitertechnik)). Um die Ausbeute zu maximieren, werden die Wafer in Reinräumen produziert.

| Bezeichnung | Ziel-Durchmesser (mm) | typische Dicke (mm) | Markteinführung (Jahr) |

|---|---|---|---|

| 1-Zoll-Wafer | ? | ? | 1960 |

| 2-Zoll-Wafer | 50,8 | 0,275 | 1971 |

| 3-Zoll-Wafer | 76,2 | 0,375 | 1973 |

| 4-Zoll-Wafer | 100 | 0,525 | 1976 |

| 5-Zoll-Wafer | 125 | 0,625 | 1982 |

| 6-Zoll-Wafer | 150 | 0,675 | 1988 |

| 8-Zoll-Wafer | 200 | 0,725 | 1990 |

| 12-Zoll-Wafer | 300 | 0,775 | 1997 |

| 18-Zoll-Wafer | 450 | 0,925 (lt. Spez.[4]) | noch unbekannt[5][6] |

Die Herstellungskosten von unstrukturierten Wafern hängen vom Durchmesser und dem Material (Silicium, Germanium, Galliumarsenid usw.) sowie dem Herstellungsverfahren (siehe unten) ab. Die Kosten für bearbeitete Wafer – sogenannte strukturierte Wafer – steigen mit der Anzahl der Prozessschritte erheblich an. Schon nach der Herstellung von STI-Strukturen haben sich die Kosten gegenüber unstrukturierten Wafern mindestens verdoppelt. Neben der Anzahl der durchgeführten Prozessschritte hängen die Kosten auch erheblich von der verwendeten Strukturgröße ab. Computerchips auf einem durchschnittlichen 200-mm-Wafer mit einer Strukturgröße von 90 nm (90-nm-Technologie) lagen Mitte 2008 bei ca. 850 Euro je Wafer. Die Produktionskosten von Spitzenprodukten (auf 300-mm-Wafern), bei AMD-Grafikkarten in 28-nm-Technologie, bei Intel-Prozessoren in 22-nm-Technologie, liegen jedoch deutlich höher. Je nach Chip-Größe lassen sich auf so einem Wafer einige Dutzend bis einige Hundert Chips herstellen. Nicht in diesen Kosten enthalten sind Aufwendungen, die nach der Chipherstellung entstehen, beispielsweise das Verpacken der Chips in Gehäuse.[7]

- Galliumarsenid-Wafer mit Micro-LED-Feldern

- Optisch teilweise transparente Siliciumcarbid-Wafer

- 450-mm-Silicium-Wafer

- 300-mm-Silicium-Wafer in einer Transportbox (FOSB)

Herstellung

Die Waferherstellung beginnt mit einem Block aus einem Halbleitermaterial, der Ingot genannt wird. Ingots können monokristallin oder polykristallin aufgebaut sein und werden zumeist mit einem der folgenden Verfahren hergestellt:

- Zonenschmelzverfahren

- Czochralski-Verfahren, u. a. das Liquid-Encapsulated-Czochralski-Verfahren (LEC-Verfahren)

- Bridgman-Stockbarger-Methode

- Vertical Gradient Freeze (VGF)

- Pedestalverfahren

- Blockgussverfahren oder Bridgman-Verfahren mit einem kontrollierten Schmelz- und Abkühlungsverlauf, für polykristallines Silicium[8]

Alle diese Verfahren liefern im Endeffekt mehr oder weniger zylinderförmige oder quadratische Ein- oder Polykristalle, die quer zu ihrer Längsachse in Scheiben, die Wafer, zersägt werden müssen. Um die Präzision für diesen speziellen Schnitt bei möglichst wenig Verschnitt zu optimieren, wurde das Innenlochtrennen entwickelt. Die Schneidblätter tragen dabei die Schneidzähne (ggf. Schneiddiamanten) auf der Innenseite einer Innenbohrung, die etwas größer als der Rohlingsdurchmesser sein muss. Mittlerweile hat sich jedoch auch das Drahtsägen, das ursprünglich nur für Solar-Wafer entwickelt wurde, mehr und mehr etabliert.

In der Literatur finden sich spezielle Wafer-Bezeichnungen, die unter anderem angeben, welches Herstellungsverfahren genutzt wurde. So werden beispielsweise Wafer, die mit dem Czochralski-Verfahren hergestellt wurden, als CZ-Wafer bezeichnet. Analog dazu wird die Bezeichnung FZ-Wafer, für Wafer, die mit dem Zonenschmelzverfahren (engl. float zone) hergestellt wurden, verwendet.

Für die meisten Anwendungen müssen die Oberflächen der Wafer optisch spiegelnd poliert sein. Dazu werden die Wafer zunächst geläppt und anschließend mittels einer chemisch-mechanischen Politur behandelt, bis die geforderte Oberflächenrauigkeit (wenige Nanometer) erreicht ist. Weitere wichtige Geometrieparameter von Wafern sind die globalen Dickenschwankungen (englisch total thickness variation, TTV), die Art und Größe der Verwölbung (engl. wafer warp) bzw. Verbiegung (engl. wafer bow) uvm.[9][10]

Europa verliert weiterhin den Anschluss bei der Wafer-Produktion. Etwa 75 % der weltweiten Produktion erfolgt in Asien, davon 16 % in China.[11]

Kennzeichnung

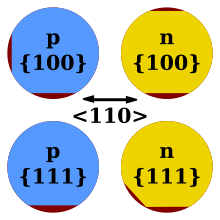

Da für die Verarbeitung der Wafer die exakte Position in der bearbeitenden Maschine wichtig ist, werden die Wafer (bei Galliumarsenid bis 125 mm Durchmesser, bei Silicium bis 150 mm Durchmesser[12]) mit sogenannten „Flats“ (engl. für »Abflachung«) gekennzeichnet. Dabei wird mit Hilfe eines primären und eventuell eines sekundären Flats angezeigt, welche Winkelorientierung vorliegt und welche Kristallorientierung die Oberfläche hat (siehe Abbildung). Bei größeren Wafern (für Silicium ab 150 mm Durchmesser[12]) werden statt der Flats sogenannte Notches (Kerben) eingesetzt. Sie bieten den Vorteil der genaueren Positionierung und verursachen vor allem weniger Verschnitt.

Heutzutage wird außerdem eine eindeutige Waferkennzeichnung als Strichcode, OCR-lesbarer Text und/oder DataMatrix-Code per Laser an eine Stelle nahe der Notch am Rand der Waferunterseite geschrieben.

In der Photovoltaik

In der Photovoltaik werden im Allgemeinen zwei Typen von Wafern unterschieden: polykristalline (auch multikristallin genannt) und monokristalline Wafer. Die Herstellung erfolgt für beide Typen durch Sägen von entsprechenden Ingots. Polykristalline Ingots werden aus quaderförmigen polykristallinen Silicium-Blöcken hergestellt, woraus sich die Form der Wafer ergibt (meist quadratisch). Monokristalline Wafer werden hingegen aus zylinderförmigen monokristallinen Ingots geschnitten, wie sie auch für mikroelektronische Anwendungen genutzt werden. Sie besitzen in der Regel eine „pseudoquadratische“ Form, d. h. mit abgerundeten Ecken. Im Unterschied zu quadratisch geschnittenen Wafern fällt bei der Erzeugung aus den runden monokristallinen Ingots weniger Verschnitt an. Ineffiziente, verschnittreiche Verfahren sind kostensteigernd und verschlechtern die Umweltbilanz. Außerdem ist der Verschnitt durch die Schneidhilfsmittel und den Drahtabrieb verunreinigt (und bildet eine Suspension) und kann nur schwer wieder zurückgewonnen werden. Andere Verfahren wie „edge-defined film-fed growth“ (EFG) der Schott Solar oder „string ribbon“ (SR) der Firma Evergreen Solar ermöglichen es, sehr dünne Wafer direkt aus der Schmelze zu ziehen.[13] Das abwasser-, energie- und abfallintensive Drahtsägen entfällt hierbei.[14] Die Waferdicke ist mit ca. 200 µm (in der aktuellen Massenproduktion) wesentlich dünner als in der Mikroelektronik. Es werden keine Polierverfahren verwendet. Aus den Wafern werden in mehreren nachfolgenden Bearbeitungsschritten Solarzellen und hieraus wiederum Solarmodule hergestellt.

- Pseudoquadratische Solarzelle aus monokristallinem Silicium

- Ein polykristalliner Wafer, wie er für Solarzellen verwendet wird

- Quadratische Silicium-Wafer bei der Solarzellen-Produktion

Weblinks

Einzelnachweise

- ↑ wafer noun. In: Oxford Advanced American Dictionary at OxfordLearnersDictionaries.com. Abgerufen am 25. Oktober 2019.

- ↑ Wafer. In: Merriam-Webster. Abgerufen am 25. Oktober 2019.

- ↑ Your Guide to SEMI Specifications for Si Wafers. (PDF; 150 kB) Virginia Semiconductor, Juni 2002, abgerufen am 20. September 2010 (englisch).

- ↑ Mark LaPedus: Industry Agrees on first 450-mm wafer standard. EETimes.com, 22. Oktober 2008.

- ↑ Graham Pitcher: In the space of five years, it looks like 450mm manufacturing has become surplus to current requirements. In: newelectronics.co.uk. 28. Juni 2016, abgerufen am 14. Dezember 2016.

- ↑ Marc Sauter: Auftragsfertiger: Intel entwickelt drei 10-nm-Prozesse und öffnet sich für ARM. In: golem.de. 17. August 2016, abgerufen am 14. Dezember 2016.

- ↑ TSMC 2008 Second Quarter Investor Conference, 31. Juli 2008 (PDF)

- ↑ Eintrag Multikristalliner Ingot = Multisilizium imGlossar ( vom 11. August 2011 im Internet Archive) zur Silicium-Wafer-Herstellung der Firma Swiss Wafers, abgerufen am 16. April 2010.

- ↑ Sami Franssila: Introduction to Microfabrication. John Wiley and Sons, 2010, ISBN 978-0-470-74983-8, S. 274–275 (Abschnitt: Wafer Mechanical Specifications).

- ↑ Thickness, Shape and Flatness Measurement of Semiconductor Wafers (PDF; 44 kB). MTI Instruments Inc. (Übersicht über die Wafer-Geometriecharakteristiken).

- ↑ China hält 16 Prozent der weltweiten Wafer-Kapazitäten.

- ↑ a b Joachim Frühauf: Werkstoffe der Mikrotechnik. Hanser Verlag, 2005, ISBN 978-3-446-22557-2, S. 60 (eingeschränkte Vorschau in der Google-Buchsuche).

- ↑ Jörn Iken: Ziehen oder Sägen – ein Systemvergleich solarenergie.com. 4. Dezember 2006, abgerufen am 16. August 2010.

- ↑ Nicole Vormann: Nachhaltigkeit und Social Responsibility in der Photovoltaik-Industrie. (Studie) Murphy&Spitz, Januar 2010, abgerufen am 4. März 2010.

Auf dieser Seite verwendete Medien

Autor/Urheber: Stephan Kambor, Lizenz: CC BY-SA 2.5

125x125 pseudo-square monocrystalline silicon solar cell, monokristaline Silizium Solarzelle

Title: Silicon single crystal

- Desc: Silicon single crystal made by Czochralski method

- Author: Twisp

- Date: 25.08.2005

Autor/Urheber: Intel Free Press, Lizenz: CC BY 2.0

Dan Hutcheson has been following the semiconductor industry for more than 30 years and ranks among the foremost independent authorities on chip making and the economics of innovation. In the early 1980s, he developed the first factory cost-of-ownership models, and more recently advised the White House Council of Economic Advisors on innovation. Intel Free Press story: What's the Outlook for the Semiconductor Industry? As 22-nanometer chips reach the market, a longtime industry observer considers the state of semiconductors today and what lies ahead.

Autor/Urheber: Palee93, Lizenz: CC BY-SA 4.0

GaN-on-Silicon processed microLED arrays on wafer

Silicon solar wafers move down a conveyor belt following a quality check.

Autor/Urheber: FDominec, Lizenz: CC BY-SA 4.0

A transport box containing two six-inch (∅150mm) wafers made of silicon carbide, to be used as substrates for homoepitaxial growth of SiC transistor layers by means of MOVPE. A ballpoint pen was added as a scale. Note the wafer transparency is about 50 % over visible spectrum, due to sub-band absorption. Also note the elliptical darker area on the upper wafer, which is a characteristic trait of the production process being used.

Autor/Urheber: Armin Kübelbeck, Lizenz: CC BY-SA 3.0

Polykristalliner texturierter Wafer mit 100x100 mm Kantenlänge, wie er zu Herstellung von Silizium-Solarzellen verwendet wird (nach dem Sägen und Texturieren)

Autor/Urheber: unknown, Lizenz: CC BY-SA 3.0

Image:Wafer 2 Zoll bis 8 Zoll.jpg uploaded by Saperaud

Autor/Urheber: Cepheiden, Lizenz: CC BY-SA 3.0

Sicht auf die Vorderseite einer FOSB-Kasette (engl.: front opening shipping box ). Die FOSB-Kasette bietet Platz für 25 300-mm-Wafer (8 der 25 Platze sind durch unterschiedlichen 300-mm-Silicium-Wafer belegt)

Wafer flats convention, based on Image:Wafer flats convention.PNG

Conventional meaning of flats in semiconductor wafers. Red denotes material that has been removed.

Wafer orientation is the orientation of the crystallographic plane in which the crystal grew. Wafer type indicated the type of doping.

Primary flat - indicates crystallographic planes of high symmetry (usually the {110} face).

Secondary flat - it's position relative to Primary flat or it's absence is indicating the doping type and the orientation of wafer.

- Absence - p {111}

- 90° - p {100}

- 180° - n {100}

- 45° - n {111}

Autor/Urheber: Jeff Keyzer from San Francisco, CA, USA, Lizenz: CC BY 2.0

Silicon wafer diameter progression vs. time.