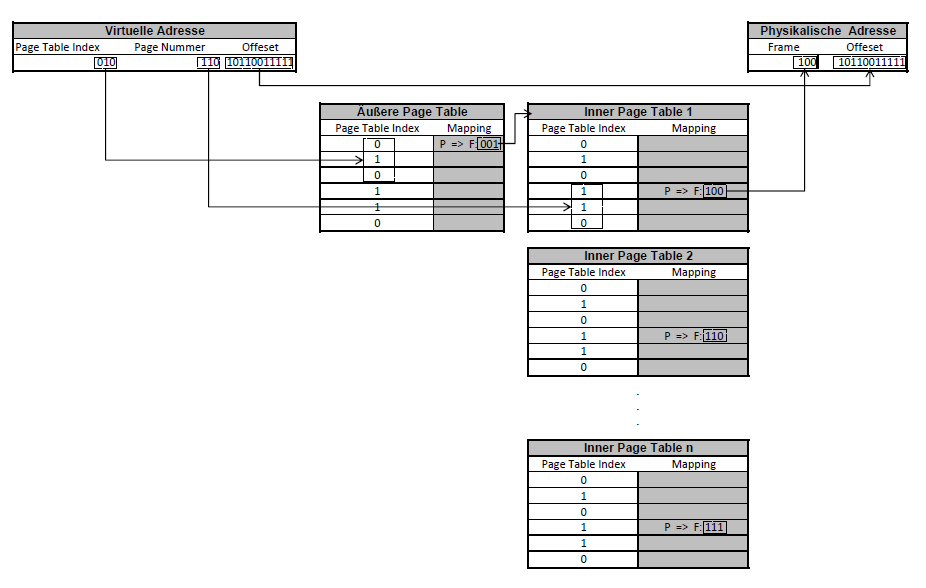

Funktionsweise des mehrstufigen Page Table Lookups bei Prozessoren

Relevante Bilder

Relevante Artikel

Second Level Address TranslationSecond Level Address Translation (SLAT), auch als Nested Paging bezeichnet, ist eine hardwareunterstützte Virtualisierungstechnologie, die eine effizientere Umsetzung von Shadow Page Tables im Vergleich zu einer softwarebasierten Virtualisierungslösung erlaubt. AMD implementierte SLAT zuerst durch eine von AMD als Rapid Virtualization Indexing (RVI) bezeichnete Technologie und unterstützt diese seit der Einführung der dritten Opteron-Prozessorgeneration 2007 in ihren Prozessoren. Mit der Nehalem-Prozessorfamilie führte Intel 2008 eine Implementierung von SLAT ein, die von Intel selbst als Extended Page Tables (EPT) bezeichnet wird. Sie wird in bestimmten Prozessoren der Core-i7-, Core-i5- und Core-i3-Klasse unterstützt. .. weiterlesen