XNOR-Gatter

| Gatter-Typen | |

|---|---|

| NOT | |

| AND | NAND |

| OR | NOR |

| XOR | XNOR |

| AOI | OAI |

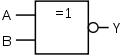

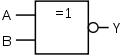

Ein XNOR-Gatter (engl. eXclusive NOT OR) ist ein Logikgatter, bei dem am Ausgang eine logische „1“ anliegt, wenn an einer geraden Anzahl von Eingängen „1“ anliegt und an den restlichen „0“. Im Fall von zwei Eingängen liegt am Ausgang also „1“ an, wenn an beiden Eingängen „1“ oder an beiden Eingängen „0“ anliegt (im zweiten Fall liegt an null Eingängen „1“ an, und 0 zählt als gerade Zahl). Die XNOR-Verknüpfung wird auch als Äquivalenz, Biimplikation oder Bikonditional bezeichnet. Es bildet zusammen mit dem XOR einen booleschen Ring ab, so wie AND mit OR und NAND mit NOR.

Übersicht

| Funktion | Schaltsymbol | Wahrheitstabelle | Relais-Logik | |||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| IEC 60617-12 | US ANSI 91-1984 | DIN 40700 (vor 1976) | ||||||||||||||||||

|  |  oder  |

|  | ||||||||||||||||

Logiksynthese

Realisierung mittels NAND oder NOR

| Verknüpfung | Mittels | Umsetzung |

|---|---|---|

x XNOR y | ||

NAND | (x NAND y) NAND ((x NAND x) NAND (y NAND y)) | |

NOR | (x NOR (x NOR y)) NOR (y NOR (x NOR y)) |

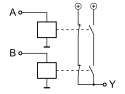

| Umsetzung mit NAND | Umsetzung mit NOR |

|---|---|

|  |

XOR und Inverter

Das XNOR-Gatter lässt sich auch durch ein Exklusiv-Oder-Gatter mit nachgeschaltetem Nicht-Gatter (Inverter) aufbauen.

AND-OR-Invert

Ein XNOR-Gatter kann mit einem NAND-Gatter mit einem nachgeschalteten OR-AND-Invert-Gatter realisiert werden. Alternativ, wenn sowohl die Ausgangssignale als auch die invertierten Signale zur Verfügung stehen (beispielsweise die Ausgänge eines Flipflops), kann es aus einem 2-2-AND-OR-Invert-Gatter aufgebaut werden.[1]

- XNOR-Implementierung mit einem NAND- und einem OAI-Gatter

- XNOR-Implementierung mit normalen und invertierten Eingängen aus einem 2-2-AND-OR-Invert-Gatter

CMOS

Mit den oben dargestellten Schemata lasen sich NAND-Gatter in CMOS realisieren, unter Verwendung von 10 bzw. 8 Transistoren.[1] Stehen die invertierten Eingänge nicht zur Verfügung, so sind vier weitere Transistoren für die Inverter erforderlich.

- Ein XNOR-Gatter in CMOS mit einem NAND- und einen OAI-Gatter

- Ein XNOR-Gatter in CMOS unter Verwendung von normalen und invertieren Eingängen aus einem 2-2-AND-OR-Invert-Gatter

Integrierte Schaltkreise

Der Baustein 4077 aus der 4000er Logikfamilie sowie der 74x7266 aus der 74er Reihe beinhalten vier XNOR-Gatter mit je zwei Eingängen.

Literatur

- Ulrich Tietze, Christoph Schenk: Halbleiter-Schaltungstechnik. 12. Auflage. Springer, 2002, ISBN 3-540-42849-6.

- Klaus Beuth: Digitaltechnik. 10. Auflage. Vogel, 1998, ISBN 3-8023-1755-6.

- Manfred Seifart, Helmut Beikirch: Digitale Schaltungen. 5. Auflage. Technik, 1998, ISBN 3-341-01198-6.

Einzelnachweise

- ↑ a b P. Fischer: Aussagenlogik und Gatter. (PDF) Universität Heidelberg, abgerufen am 21. Januar 2024.

Auf dieser Seite verwendete Medien

Autor/Urheber: Trex4321, Lizenz: CC0

One of the alternative implementations of XNOR, using a NAND and an OR-AND-Invert gate. This is an efficient implementation for logic families like CMOS or TTL.

A way of building an XNOR gate from only NAND gates, using the expression . This construction has a propagation delay 3 times that of a single gate and uses 5 gates.

A way of building an XOR gate from only NOR gates. This construction has a propagation delay 3 times that of a single NOR gate and uses 4 gates.

Autor/Urheber: Rk sTEk, Lizenz: CC BY-SA 3.0

Symbol für XNOR-Gatter nach DIN 40700 (veraltet), jedoch kein Teil des Standards - Variante 2

logic XNOR gate

Autor/Urheber: Trex4321, Lizenz: CC0

This is an XNOR gate using AOI logic, which uses both inputs and inverted inputs.

Autor/Urheber: Rk sTEk, Lizenz: CC BY-SA 3.0

Symbol für XNOR-Gatter nach DIN 40700 (veraltet), jedoch kein Teil des Standards - Variante 1

Autor/Urheber: Rk sTEk, Lizenz: CC BY-SA 3.0

XNOR in Relais-Logik - berichtigte Version

Autor/Urheber: Trex4321, Lizenz: CC0

An implementation of an XNOR gate which uses inverted inputs and a 2-2 AOI gate.

Autor/Urheber: Trex4321, Lizenz: CC0

This is a CMOS implementation of an XNOR gate using a NAND gate (left) and a 2-1 OR-AND-Invert gate (right.