Static random-access memory

Static random-access memory (deutsch: statisches RAM, Abkürzung: SRAM) bezeichnet einen elektronischen Speicherbaustein. Zusammen mit dem dynamischen RAM (DRAM) bildet es die Gruppe der flüchtigen (volatil; engl. volatile) Speicher, das heißt, die gespeicherte Information geht bei Abschaltung der Betriebsspannung verloren. Im Gegensatz zu DRAM benötigt der SRAM kein periodisches (dynamisches) Auffrischen (engl. refresh) zur Vermeidung von Datenverlust in jeder Datenzelle, sondern behält seine Dateninformation, solange die Betriebsspannung anliegt.

Geschichte

Im Jahre 1963 entwarf der bei Fairchild Semiconductor tätige Elektroingenieur Robert Norman das Prinzip einer Speicherzelle in bipolarer Planartechnik und meldete dies zum Patent an.[1] Ein Jahr später entwickelte John Schmidt, ebenfalls bei Fairchild Semiconductor, einen SRAM-Baustein mit 64 Bit Speicherkapazität in P-Kanal-MOS-Technik, die in Speichermodulen mit 1024 Bit in Rechnern der Firma Burroughs zum Einsatz kamen.[2]

Nach der Gründung der Firma Intel durch zwei ehemalige Fairchild-Mitarbeiter im Jahre 1968 wurde im April 1969 mit dem Intel 3101 als erstes Produkt ein SRAM-Speicherbaustein mit 64 Bit Speicherkapazität in bipolarer Schottky-Technik vorgestellt.[3]:2–87 Drei Monate darauf erschien der in P-MOS Technik gebaute Intel 1101 mit 256 Bit Speicherkapazität[3]:2–4, der Stromverbrauch pro Bit konnte auf ein Viertel reduziert werden.[3]:2–2f

Die SRAM-Speicherbausteine versprachen einen großen Kostenvorteil gegenüber der bis dahin als Hauptspeicher genutzten Kernspeichertechnik.[2] Für den Einsatz als Hauptspeicher stand aber bereits im Oktober 1970 mit dem ersten DRAM-Speicher, dem Intel-1103, eine schnellere und günstigere Alternative mit wesentlich geringerem Stromverbrauch[3]:2–2 zur Verfügung. Der Intel 1103 DRAM benötigte drei Transistoren pro Speicherzelle, während im Intel 1101 SRAM sechs Transistoren pro Speicherzelle nötig waren.

Eigenschaften und Aufbau

SRAM behält Daten in seinem Speicher, solange Strom zugeführt wird. Im Gegensatz zu DRAM, der kontinuierlich aktualisiert werden muss, besteht bei SRAM diese Anforderung nicht. Allerdings ist SRAM auch teurer als DRAM und benötigt mehr Platz. SRAM verwendet Flipflops anstelle von Kondensatoren, um Daten in Form von Bits zu speichern. SRAM benötigt im Vergleich zu DRAM mehr Energie. Der Einsatz von SRAM führt also zu einem höheren Stromverbrauch.

SRAM ist schneller als andere Arten von elektronischen Speicherbausteinen. Weil SRAM außerdem keine zeitaufwändigen Aktualisierungszyklen erfordert, ermöglicht es schnellen Datenzugriff und bietet geringere Latenzzeit. Diese beiden Eigenschaften machen SRAM ideal für Anwendungen, bei denen Geschwindigkeit entscheidend ist. Datenintegrität ist ein weiterer Bereich, in dem SRAM gegenüber einigen anderen Speichertypen im Vorteil ist. Die Integrität der Daten bleibt durchgängig erhalten, da SRAM keine Kondensatoren verwendet und auch keine ständige Aktualisierung erfordert. Mittlerweile sind moderne SRAMs erhältlich, die Techniken wie Power Gating und dynamische Spannungsskalierung verwenden. Dadurch verbraucht es weniger Strom und ist energieeffizienter als seine Vorgänger. Trotzdem eignet sich SRAM am besten für Anwendungen, bei denen Energieeffizienz weniger Priorität hat als hohe Zugriffsgeschwindigkeiten und Reaktionsfähigkeit, geringe Latenzzeit und Datenintegrität. SRAM erzeugt außerdem weniger Wärme und ist strahlungsbeständiger.[4]

Die Informationen werden durch Zustandsänderung einer bistabilen Kippstufe in Form eines Flipflops pro Bit gespeichert. Das erlaubt es zwar, die Speicherzelle schnell auszulesen, aber im Vergleich zu dynamischen Speicherzellen ist die Speicherzelle verhältnismäßig groß und daher die Speicherkapazität des gesamten Chips entsprechend kleiner. Im statischen Betrieb (Halten der Information) ist der Leistungsbedarf einer Zelle sehr klein.

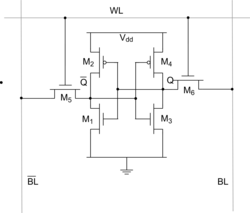

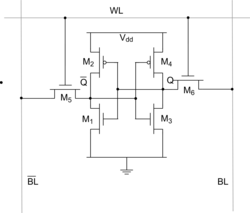

SRAMs werden heutzutage meist als 6-Transistor-Zelle (6T-SRAM-Zelle) in CMOS-Technik hergestellt. Der Aufbau einer Kippstufe mit Widerständen als Lastelementen (sogenannte 4T-SRAM-Zelle) wird nicht mehr eingesetzt; statt der Lastwiderstände werden heute p-Kanal-MOS-Transistoren verwendet. Mit weiteren zwei Transistoren zur Ankopplung an die Spalten- bzw. Zeilen-Auswahlleitungen ergibt sich die besagte 6-Transistor-Zelle wie im Bild anbei. Wegen dieses komplizierteren Aufbaus verbraucht eine SRAM-Zelle im Vergleich zu einer DRAM-Zelle deutlich mehr Chipfläche (über 140 F²).[5][6] Prinzipiell wird also jedes Bit in der SRAM-Zelle in vier Transistoren gespeichert, die zwei gegeneinander verschaltete Inverter bilden. Diese Speicherzelle hat zwei stabile Zustände, die 0 und 1 darstellen. Die beiden zusätzlichen Zugriffstransistoren werden benutzt, um den Zugriff auf die Speicherzelle während Lese- und Schreibzugriff zu steuern.

Neben dem 4T- und 6T-SRAM-Design gibt es noch zahlreiche alternative Varianten, die mithilfe weiterer Transistoren zusätzliche Funktionen (zum Beispiel separater Leseport) oder besondere Eigenschaften (zum Beispiel geringere Leckströme, geringere Leistungsaufnahme beim Schreiben, höhere Stabilität[7]) realisieren sollen. Die hierfür genutzten Bezeichnungen 5T-, 7T-, 8T-, 9T-, 10T- oder 12T-SRAM-Zelle sind jedoch nicht auf ein spezielles Design beschränkt, vgl.[8]

Funktionsweise

Eine SRAM-Zelle besitzt drei unterschiedliche Zustände. Diese sind: Standby (warten auf Zugriff), Lesezugriff (Speicherzustand wurde angefordert) und Schreibzugriff (Speicherzustand wird überschrieben). Diese Zustände funktionieren wie folgt:

Standby

Wenn die Wordline nicht geschaltet ist, trennen die Zugriffstransistoren die Speicherzelle von den Bitlines. Die beiden gegenverschalteten Inverter (Transistoren M1-M4) verstärken ihren aktuellen Zustand jeweils gegenseitig (solange die Betriebsspannung anliegt).

Lesezugriff

Wir nehmen an, dass der Speicherzustand bei Q auf logisch 1 gesetzt ist. Der Lesezugriff startet dann mit dem Aufladen der beiden Bitlines auf die Hälfte der Betriebsspannung, gefolgt von dem Schalten der Wordline, um beide Zugriffstransistoren durchzuschalten. Als zweiten Schritt werden dann die jeweiligen Werte von Q und Q auf die Bitlines übertragen, d. h. BL bleibt aufgeladen und BL wird über M1 und M5 zu einer logischen 0 entladen (M1 ist aktiviert, weil Q auf eine logische 1 gesetzt ist). BL wird durch M4 und M6 über die Versorgungsspannung auf der logischen 1 geladen. Wenn der Speicherzustand vorher 0 gewesen wäre, wäre das Verhalten entsprechend entgegengesetzt. Der Unterschied zwischen BL und BL kann dann durch einen Leseverstärker ausgelesen werden.

Schreibzugriff

Der Schreibzugriff beginnt damit, dass der zu schreibende Wert auf die Bitlines gelegt wird. Wenn wir also eine 0 schreiben wollen, wird BL auf 0 und BL auf 1 gesetzt. Beim Schreiben einer 1 werden die beiden Werte vertauscht. In der Folge wird dann die Wordline geschaltet, so dass der Wert in die Speicherzelle geschrieben wird. Dies funktioniert, weil die relativ schwachen Transistoren, die die Inverter bilden, durch die relativ starken Bitlines überschrieben werden können. Eine entsprechende Größenauslegung der Transistoren ist bei der Herstellung notwendig, damit das Überschreiben einwandfrei funktioniert.

Arten von SRAM

Es gibt viele Arten von SRAM mit unterschiedlichen Designs und für unterschiedliche Anwendungen entwickelt. Der gebräuchlichste Typ ist binärer SRAM, bei dem eine Speicherzelle ein Bit in einem von zwei binären Zuständen speichert. Dieses SRAM eignet sich am besten für Anwendungen, die geringe Latenzzeit und schnellen Datenzugriff erfordern. Ternärer SRAM speichert drei Zustände pro Zelle und bietet so eine höhere Datendichte und effizientere Lesevorgänge und Schreibvorgänge. SRAM ist auch in synchronen und asynchronen Varianten erhältlich. Synchrones SRAM ist mit der Systemuhr synchronisiert, während asynchroner SRAM nicht synchron mit der Systemuhr arbeitet. Erstere eignet sich für die digitale Hochgeschwindigkeitssignalverarbeitung in der digitalen Kommunikation und anderen Anwendungen, bei denen die Datentaktung zwischen SRAM und Systemuhr präzise koordiniert werden muss. Letztere eignet sich am besten für Hochgeschwindigkeitsanwendungen. Quad Data Rate SRAM ist ein spezieller Typ synchroner SRAM, der hohe Geschwindigkeit und Effizienz bietet, indem er den Datenzugriff mit den steigenden und fallenden Flanken des Systemtaktsignals synchronisiert.

Schnittstellen

SRAMs werden mit unterschiedlichen Schnittstellen angeboten. Als diskretes Bauelement, primär für den direkten Anschluss an Mikrocontrollern, kommen parallele asynchrone Busschnittstellen zur Anwendung. Merkmal ist, dass der Zugriff auf den Speicher ohne Taktsignal erfolgt. Die Zugriffszeit pro Speicherzelle richtet sich nach der Laufzeit und liegt im Bereich von 5 ns bis zu knapp 100 ns. Darüber hinaus gibt es synchrone SRAMs, bei welchen der Zugriff synchron zu einem Taktsignal erfolgt. Im Regelfall ist der Durchsatz von synchronen SRAMs höher als bei asynchronen SRAMs, da bei synchronen Schnittstellen die Möglichkeit besteht, mittels einer Pipeline die Adressen zu den Daten definiert zeitlich zu versetzen. Dies bringt vor allem bei sequenziellen Speicherzugriffen Geschwindigkeitsvorteile. Ein Beispiel von synchronen SRAMs sind die sogenannten „ZBT-SRAMs“ (engl. zero-bus-turnaround SRAM), welche bei schnellen Grafikspeichern Anwendung finden.[9] Für den Einsatz in Kombination mit DDR- und „Quad“-Speicher gibt es auch SRAMs, die entsprechend mehr Daten auf beiden Flanken des Taktsignals übertragen; hierbei werden Größen bis 144 Mibit (in der Organisation 8 Mi×18) bei einer Taktfrequenz von 1066 MHz erreicht.

Anwendungen

Aufgrund seiner Kosten und Größe wird SRAM normalerweise nicht als Hauptspeicher eines Computers verwendet. Die meisten Computer verwenden stattdessen DRAM, da es höhere Datendichten bei geringeren Kosten unterstützt. SRAM kann Teil eines Digital-Analog-Umsetzers auf der Videokarte oder Grafikkarte eines Computers sein. Es kann auch in einem Festplattenlaufwerk als Puffercache verwendet werden, in einem Peripheriegerät wie einem Drucker oder einer Flüssigkristallanzeige oder in einem Netzwerkgerät wie einem Router oder Switch. Die häufigsten Verwendungszwecke von SRAM sind der Cache-Speicher eines Computers, beispielsweise der Prozessor-Cache, und Hochgeschwindigkeitsregister. SRAM ist auch in anderen Geräten zu finden. Beispielsweise werden SRAM-Chips häufig in Mobiltelefonen, Wearables und anderen Unterhaltungselektronikgeräten verwendet. Sie können auch in medizinische Produkte eingebettet sein, die alles von Hörgeräten bis hin zu Body Area Networks umfassen können, die aus mehreren im Körper eingebetteten Geräten bestehen. In all diesen Geräten ist ein schneller Datenzugriff unerlässlich, weshalb SRAM besser geeignet ist als DRAM oder nichtflüchtiger Flash-Speicher. Darüber hinaus wird SRAM in Spielzeugen, Haushaltsgeräten, Autos, Industrieanlagen und Geräten des Internet der Dinge verwendet.[4]

SRAMs finden als schneller Speicher mit vergleichsweise kleiner Datenkapazität überall dort Anwendung, wo der Dateninhalt schnell im Zugriff sein muss, wie beispielsweise in Prozessoren als Cache und auf digitalen oder Mixed-Signal-ICs wie FPGAs als lokaler Speicher auf dem Chip.

Etwa in den 1980er Jahren benötigten die Mikroprozessoren SRAMs als externen Arbeitsspeicher, da sie keinen integrierten Arbeitsspeicher hatten. Die typischen Bausteine waren 5101 (noch zu vier Bit organisiert, Nibble genannt), 6116 und 6264.

Weiterhin wird SRAM in Geräten eingesetzt, bei denen der Dateninhalt ohne dauerhafte Stromversorgung bis zu einigen Jahren gesichert werden soll. Da der Stromverbrauch im statischen Zustand (keine Speicherzugriffe) im Bereich einiger nA liegt, genügt eine kleine Pufferbatterie (u. U. auch ein Kondensator), um die nötige Versorgungsspannung bereitzustellen, beispielsweise beim CMOS-RAM zur Speicherung von BIOS-Einstellungen in handelsüblichen PCs. In diesem Anwendungsbereich stellt das SRAM in Kombination mit einer meist in Form einer Lithiumbatterie ausgeführten Pufferbatterie eine spezielle Form von NVRAM (engl. non-volatile random-access memory, nicht-flüchtiger RAM) dar. Die Batterie kann in das Chipgehäuse des Speicherbausteins integriert sein.[10]

Literatur

- Ulrich Tietze, Christoph Schenk: Halbleiter-Schaltungstechnik. 12. Auflage. Springer, Berlin 2002, ISBN 3-540-42849-6, Statische RAMs, S. 713 ff.

- Jörg Schulze: Konzepte siliziumbasierter MOS-Bauelemente. Springer, Berlin 2005, ISBN 3-540-23437-3, S. 66–67, 297–314.

Einzelnachweise

- ↑ Patent US3562721A: Solid State Switching and Memory Apparatus. Angemeldet am 5. März 1963, veröffentlicht am 9. Februar 1971, Anmelder: Fairchild Camera and Instrument Corporation, Erfinder: Robert H. Norman.

- ↑ a b 1970: MOS Dynamic RAM Competes with Magnetic Core Memory on Price. (pdf) Computer History Museum, abgerufen am 12. November 2023 (englisch).

- ↑ a b c d intel data catalog 1976. (pdf) Abgerufen am 12. November 2023 (englisch).

- ↑ a b TechTarget: What is SRAM (static random access memory)?

- ↑ The International Technology Roadmap for Semiconductors 2007 – Emerging Research Devices ( vom 26. März 2010 im Internet Archive), Seite 7 (engl., PDF; 1,1 MB)

- ↑ The International Technology Roadmap for Semiconductors 2007 – System Drivers ( vom 6. März 2009 im Internet Archive) (engl., PDF; 603 kB)

- ↑ L. Chang u. a.: Stable SRAM cell design for the 32 nm node and beyond. In: 2005 Symposium on VLSI Technology, 2005. Digest of Technical Papers. 2005, S. 128–129, doi:10.1109/.2005.1469239 (PDF).

- ↑ Forrest Brewer: Array Structured Memories. (PDF; 2,3 MB) In: VLSI Project Design, ECE 224A – Spring 2011. Abgerufen am 1. April 2013 (Vortragsfolien).

- ↑ 71T75602 – 2.5V 512K X 36 ZBT Synchronous 2.5V I/O PipeLine SRAM. Renesas, abgerufen am 9. Januar 2022 (englisch, Datenblatt eines synchronen ZBT-SRAMs mit 512 Ki × 36).

- ↑ Datenblatt ( vom 1. Januar 2010 im Internet Archive) (PDF; 178 kB) eines NV-SRAM. (DS2030 mit 32 Ki × 8 mit integrierter Pufferbatterie) (englisch)

Auf dieser Seite verwendete Medien

Circuit diagram of an SRAM cell, built with four MOSFETs and two resisitors. The bulk connection of all transistors is to ground, but is not shown from simplicity.

© Raimond Spekking / CC BY-SA 4.0 (via Wikimedia Commons)

Hynix HY62V8100B - 128K x8 bit 3.3V Low Power CMOS slow SRAM