Speichermodul

Ein Speichermodul oder Speicherriegel ist eine kleine Leiterplatte, auf der mehrere Speicherbausteine (Dynamic Random Access Memory in Form von integrierten Schaltkreisen) aufgelötet sind. Speichermodule bilden oder erweitern den Arbeitsspeicher elektronischer Geräte wie Computer oder Drucker und werden dort in speziell dafür vorgesehene Steckplätze gesteckt.

Die Bezeichnung Speichermodul wird seltener auch für Speicherkarten oder USB-Sticks verwendet.

Bauformen

Handelsübliche Modul-Bauformen für Personal Computer sind oder waren:

- Single Inline Memory Module (SIMM): Dieses hat nur eine Reihe von Leitungen. Jede davon ist auf beiden Seiten durch einen Kontakt vertreten.

- 8 bit breite Module (30 Kontakte) Diese gab es auch in einer Variante mit Anschlusspins; sie wird als Single Inline Pin Package (SIPP) bezeichnet und entspricht praktisch einem SIMM mit an die Kontaktflächen angelöteten Anschlussstifte.

- PS/2-SIMM, 32 bit breit, 72 Kontakte, bestückt mit

- Fast Page Mode Random Access Memory (FPM-RAM) oder

- Extended Data Output Random Access Memory (EDO-RAM)

- Dual Inline Memory Module (DIMM): Hier sind die Kontakte beider Seiten unabhängig voneinander, 64 bit breit, bestückt mit:

- Synchronous Dynamic Random Access Memory (SDRAM)

- Double Data Rate SDRAM (DDR-SDRAM)

- Double Data Rate 2 SDRAM (DDR2-SDRAM)

- Double Data Rate 3 SDRAM (DDR3-SDRAM)

- Double Data Rate 4 SDRAM (DDR4-SDRAM)

- Small Outline Dual Inline Memory Module (SO-DIMM) für geringeren Platzbedarf (beispielsweise in Notebooks)

- Micro Dual-Inline Memory Module (Micro-DIMM)

- Rambus Inline Memory Module (RIMM): 16 bit breit

- Small Outline Rambus Inline Memory Module (SO-RIMM)

Herstellerabhängige Modulformen (beispielsweise für Server) und solche für besondere Anforderungen gibt es in großer Zahl, darunter auch DIMMs mit EDO-RAM. Andererseits verwenden andere Gerätetypen (Drucker, RAID-Controller) durchaus gängige PC-Module.

SIMM-Speichermodule (asynchron) sind „unbuffered“ oder „buffered“, DIMM-Speichermodule (synchron, SDR, DDR) entsprechend „unregistered“ oder „registered“. Als Weiterentwicklung der registered-Module sind DDR2- und DDR3-Module als Fully Buffered DIMM (FB-DIMM) eingeführt worden.

Gepufferte Module (buffered, registered, fully-buffered) sind beim Zugriff durch die Latenz des Puffers einen Taktzyklus langsamer, dafür sinkt die elektrische Belastung des Speicherinterfaces im Chipsatz bzw. im Hauptprozessor. Dies macht solche Module, insbesondere für Serveranwendungen mit großem Speicherausbau, durch eine höhere Anzahl von Speichermodulen sinnvoll.

Parameter eines Speichers

Speicherkapazität

Die Speicherkapazität eines Speichermoduls ergibt sich normalerweise als Produkt aus der Speicherkapazität der meist gleichartigen Speicherchips und deren Anzahl.

Beispiel:

Ein Speichermodul sei mit 16 Chips des Typs GM72V16821CT10K bestückt. Im Datenblatt dieses Chip ist angegeben, das er in zwei Bänken mit je 524.288 (= 219) Datenwörtern mit einer Wortbreite von jeweils 16 bit organisiert ist (2×219×16). Daraus ergibt sich eine Speicherkapazität pro Chip von 2×219×16 bit = 224 bit = 16.777.216 bit. Mit 16 dieser Chips ergibt sich eine Speicherkapazität des Speichermoduls von 224×16 = 228 bit = 268.435.456 bit; mit acht Bits pro Byte sind das 2(28-3) Byte = 33.554.432 Byte = 32 MiB.

Manche Speichermodule besitzen ein oder zwei zusätzliche Chips (gleichen oder anderen Typs), die Informationen für eine Fehlerkorrektur- bzw. Paritätsfunktion speichern. Hier werden für ein Byte häufig neun Bits verwendet (acht Datenbits und ein Prüfbit).

Leitungen

Der heute veraltete DDR/DDR2-Speicher besitzt 64 Daten-Signalleitungen (beziehungsweise 72 bei ECC). Die einzelnen SDRAM-Chips sind so verschaltet, dass sie die gesamte Breite des Datenbusses belegen. Jeder Chip ist für bestimmte Datenleitungen zuständig. Ein Chip mit einer „×n“-Organisation kann n Datenleitungen versorgen. Für einen Datenbus mit 64 Leitungen sind folglich 64/n Chips mit der Organisation „×n“ erforderlich. Bei Modulen mit mehreren Bänken (siehe unten) sind mehrere Chips (zwei oder vier) an den Datenleitungen parallel geschaltet. Folglich enthält ein Modul mit k Bänken 64/n×k Chips mit der Organisation „×n“.

Zusätzliche Eingangsleitungen regeln die Auswahl des Speicherbausteins (Chip Select) und die Schreib- bzw. Leserichtung (R/W) der Daten.

Geschwindigkeit

Ebenso wie bei der Größe, wird auch bei der Geschwindigkeit zwischen dem gesamten DIMM und den einzelnen Chips unterschieden. Ein einzelner Chip bezieht sich immer auf die maximale Taktfrequenz (zum Beispiel DDR2-1066, DDR-400, SDRAM 133).

Beim gesamten DIMM hingegen geht es um die Datentransferrate (zum Beispiel PC2-4200, PC3200). Bestückt mit SDRAM-Chips mit DDR2-533, die also eine Taktfrequenz von 266 MHz haben, übertragen sie im DDR2-Modus 4 Datenwörter pro Takt, und man kann die maximale Übertragungsrate beispielsweise folgendermaßen berechnen:

- 64 Leitungen je Speichermodul können pro Takt 4 × 8 Byte = 32 Byte übertragen;

- 133,3 Millionen Taktzyklen/s (MHz) × 32 Byte = 4,266 Milliarden Byte/s, also ungefähr 4,2 GB/s.

Der Datentransfer-Leistungswert ist nur ein Idealwert und wird in der Praxis nie erreicht. Er ist jedoch zur Klassifizierung von Speicher üblich; im obigen Beispiel wäre es also PC2-4200 aus DDR2-533-Chips, die mit 133 MHz laufen (siehe DDR2-SDRAM).

Bänke/Ranks

Ein DIMM lässt sich mit einer unterschiedlichen Anzahl jeweils gleicher Module aufbauen. Das Gremium der JEDEC Solid State Technology Association macht dabei ganz bestimmte Vorgaben zum Aufbau der DIMMs. Erlaubt ist es, Chips einzusetzen, die entweder vier (nur mit Puffer), acht oder 16 Datenleitungen (siehe oben: Leitungen) in Anspruch nehmen. Des Weiteren ist immer eine bestimmte Gruppe von DRAM-Chips jeweils einer Bank zugeordnet. Eine Bank oder ein Rank (gemäß JEDEC-Terminologie) ist dabei ein eindeutiger, unabhängig adressierbarer 64 bit breiter Bereich eines Speichermoduls (bei ECC-Modulen 72 bit).[1][2] Jede Bank verhält sich dabei wie ein separates Speichermodul. Daher belasten beispielsweise Zwei-Bank-Module die Busleitungen genau so stark wie zwei Ein-Bank-Module. Es existieren Speichermodule mit einer Bank, zwei oder vier Bänken (Single-, Dual- und Quad-Rank-DIMMs). Da Chipsätze in der Regel nur maximal acht Bänke verwalten können (bzw. bei hohem Tempo wie DDR-400 zumeist nur sechs Bänke), muss man für großen Speicherausbau (zum Beispiel 8 × 2 GiB = 16 GiB) auf Ein-Bank-Module zurückgreifen, da mit Zwei-Bank-Modulen mit 4 × 2 Bänken bereits alle acht Bänke belegt wären. Zudem muss in solchen Fällen meist die Geschwindigkeit der RAMs reduziert werden, zum Beispiel von PC3200 auf PC2700, da ansonsten die Interferenzen auf den Leitungen zu groß werden.

Zwischen der Bankanzahl und der einseitigen oder beidseitigen Bestückung der Speichermodule mit Speicherchips (single-sided/double-sided) besteht kein direkter Zusammenhang, d. h. einseitig bestückte Module können zwei Bänke enthalten, und beidseitig bestückte Module können auch nur eine Bank enthalten.

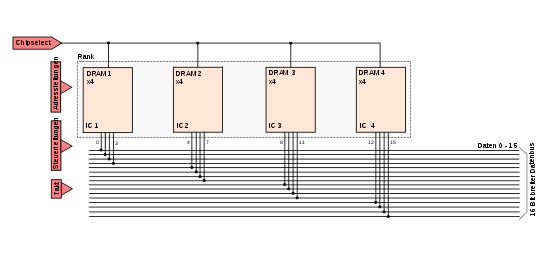

- DRAM-Modul mit einer Bank:

Die Bank besteht aus vier DRAM-Bausteinen und wird über das ChipSelect-Signal aktiviert. - DRAM-Modul mit zwei Bänken:

Jede Bank besteht aus vier DRAM-Bausteinen mit je vier Datenleitungen (×4).

Die jeweilige Bank wird zum Lesen/Schreiben über die ChipSelect 0/1-Signale ausgewählt.

Puffer

RAM-Chips gibt es mit unterschiedlichen Busbreiten (4 bit, 8 bit oder 16 bit) und in unterschiedlichen Größen (2015: 4 Gbit, 8 Gbit oder 16 Gbit)[3]. Für den Bau kleiner Module (2 GB) werden wenige kleine RAM-Chip-Bausteine mit breitem Bus benötigt (4 Stück 256M×16 bit). Jeder dieser RAM-Chip-Bausteine hängt an den Adress- und Steuerleitungen (das sind hier vier), an den Datenleitungen hängt jeweils ein RAM-Chip-Baustein.

Für größere RAM-Module werden größere RAM-Chip-Bausteine (8 Gbit, 16 Gbit) und höhere Bausteinanzahl (8, 16, 32) verwendet und entsprechend die Busbreite verringert (8 bit, dann 4 bit). Durch die höhere Chipanzahl steigt auch die Belastung der Adress- und Steuerleitungen. Ab neun Chips müssen die Adress- und Steuerleitungen mit Registern gepuffert werden; dieser Modultyp wird as RDIMM (Registered DIMM) bezeichnet. Übersteigt die Gesamtbusbreite aller Module 64/72 bit, müssen auch Datenleitungen parallelgeschaltet werden. Das kann eine zusätzliche Pufferung der Datenleitungen empfehlenswert oder notwendig machen; der Modultyp lautet dann LRDIMM (Load Reduced DIMM).

| Modulgröße | Speicherbaustein | Fan-Out | Bemerkungen | ||

|---|---|---|---|---|---|

| Anzahl | Typ (Gesamt) | Adressen | Daten | ||

| 2 GiB | 4× | 256 M × 16 bit (4 Gbit) | 4 | 1 | Kleinstes Modul mit DDR4-RAM |

| 4 GiB | 8× | 512 M × 8 bit (4 Gbit) | 8 | 1 | Erweiterung durch mehr Chips |

| 4 GiB | 4× | 512 M × 16 bit (8 Gbit) | 4 | 1 | Erweiterung durch größeren Chip |

| 16 GiB | 8× | 2 G × 8 bit (16 Gbit) | 8 | 1 | Fan-Out der Adressen von 8, größtes Modul, das als unbuffered DIMM (UDIMM) verfügbar ist |

| 16 GiB ECC | 9× | 2 G × 8 bit (16 Gbit) | 9 | 1 | Version mit ECC |

| 32 GiB | 16× a | 4 G × 4 bit (16 Gbit) | 16 | 1 | Fan-Out der Adressen von 16, erfordert Pufferung der Adressen (RDIMM: Registered DIMM) |

| 32 GiB ECC | 18× a | 4 G × 4 bit (16 Gbit) | 18 | 1 | Version mit ECC |

| 64 GiB ECC | 36× a | 4 G × 4 bit (16 Gbit) | 36 | 2 | Fan-Out der Adressen von 36, erfordert Pufferung der Adressen (RDIMM: Registered DIMM). Fan-Out der Daten von 2, wenn Daten auch gepuffert werden, handelt es sich um (LRDIMM: Load Reduced DIMM). |

Registered DIMM und Load Reduced DIMM weisen auf Grund der zusätzlichen Latenzen der Pufferbausteine größere Latenzen auf.

Funktionsweise der Adressierung

Der Auslöser für einen Schreib- oder Lesevorgang im Hauptspeicher ist hauptsächlich der Hauptprozessor. Auch Computerperipherie kann per Direct Memory Access auf den Speicher zugreifen, jedoch werden auch dabei die meisten Operationen vom Hauptprozessor veranlasst.

Findet der Hauptprozessor Daten nicht innerhalb des Prozessorcaches oder will Daten direkt in den Speicher schreiben, wird der Speichercontroller damit beauftragt. Bei älteren Intel-Prozessoren wie zum Beispiel dem Pentium 4 oder dem Core 2 Duo wurden die Befehle über den Front Side Bus an den Speichercontroller, welcher in der Northbridge sitzt, geschickt. Neuere Intel-Prozessoren wie Modelle der Core-i-Serie sowie AMD-Prozessoren seit Einführung der K8-Architektur haben einen deutlich kürzeren Weg, da hier der Speichercontroller direkt in dem Hauptprozessor liegt.

Timing

Es existiert eine Vielzahl von Parametern, welche das Zeitverhalten des Speichers steuern. Standardmäßig ist im Speichermodul ein vom Hersteller eingestelltes Zeitverhalten eingetragen. Bei modernen Bauformen befindet sich dazu ein Electrically Erasable Programmable Read-Only Memory (EEPROM) auf dem Modul, das vom BIOS ausgelesen werden kann und so für eine korrekte Konfiguration sorgt. Durch sogenanntes Tuning durch den Nutzer wird oft versucht, dieses Zeitverhalten zu optimieren, was aber zu Systemabstürzen führen kann.

DDR-Speicher wird auf die folgende Art beschriftet:

| Geschwindigkeit | Puffer | tCL | tRCD | tRP | SPD-EEPROM-Version | Platinen-Version |

|---|---|---|---|---|---|---|

| PC3200 | U | 30 | 3 | 3 | 1 | A1 |

Im obigen Beispiel wird ein Modul mit den Parametern PC3200U-30331-A1 beschrieben. Der wichtigste Parameter ist die maximale Geschwindigkeit des Moduls. „PC3200“ kennzeichnet, wie bei Geschwindigkeiten näher erklärt, Speichermodule, die 3,2 Milliarden Bytes pro Sekunde liefern können. Dadurch kann man recht einfach die Zuordnung von Prozessoren/Chipsätzen und passenden Speichermodulen ermitteln. Ein FSB-400-Prozessor kann ebenfalls nur 3,2 GB/s über seine Schnittstelle schicken. Aus diesem Grund wäre deshalb dieser Speicher für den entsprechenden Prozessor ausreichend. Das „U“ steht für ungepufferte DIMMs. Nach dem Bindestrich folgen die wichtigen Latenzzeiten und zwar ausgedrückt in Taktzyklen:

- CAS Latency tCL: Zeitdauer zwischen einem Lesekommando und dem Erhalt der Lesedaten

- RAS-to-CAS Delay tRCD: (minimale) Zeitdauer zwischen der Aktivierung einer Zeile / einer Bank und der Absendung eines Lese- oder Schreibkommandos.

- RAS Precharge Time tRP: (minimale) Zeitdauer zwischen der Deaktivierung einer Zeile / einer Bank und der erneuten Aktivierung einer Zeile in derselben Bank.

Bei DDR-SDRAM gibt es Chips mit einer CL von 2, 2,5 oder 3 Takten Dauer, weshalb man für den CL-Parameter zwei Ziffern benötigt (3033 steht für 3,0 – 3 – 3).

DDR2-Speicher wird auf die folgende Art beschriftet:

| Kapazität | DIMM-Aufbau | Geschwindigkeit | Puffer | tCL | tRCD | tRP | SPD-EEPROM-Version | Platinen-Version |

|---|---|---|---|---|---|---|---|---|

| 512 MiB | bRxc | PC2-3200 | U | 3 | 3 | 3 | 1 | A1 |

Bei DDR2-Speicher sind nur ganzzahlige Zeiten erlaubt, weshalb der CL mit nur einer Zahl angegeben wird. In der JEDEC-Spezifikation ist nur für DDR2-Speicher die Kapazitätsgröße vorgesehen. Des Weiteren wird die Angabe zum Aufbau des Riegels verlangt. „1Rx8“ steht für einen Single-Rank-DIMM, welches (x8)SDRAMs enthält (siehe Bank), wobei jeder davon acht Datenanschlüsse besitzt.

Interessante Parameter sind auch die Betriebsspannung samt Toleranzbereich, Temperatur-Grenzwerte oder weitere Latenzzeiten wie tRAS oder tRC. Solche Parameter sind in der JEDEC-Spezifikation exakt festgelegt und werden deshalb nicht extra ausgewiesen. Die Activate-to-Precharge-Zeit tRAS wird doch gerne angegeben, weil sie für Übertakter interessant ist. Sie steht meist hinter tRP durch einen Bindestrich getrennt, zum Beispiel PC3200-2022-5.

Für Übertakter auch interessant ist die Command Rate (1T/2T), obwohl diese Latenzzeit des Speicherchips keine isolierte Eigenschaft ist. Diese Wartezeit wird dann nötig, wenn viele Chips am Speicherkanal aktiv sind und dadurch die Adressleitungen des Speichercontrollers stärker belastet werden. In der Regel lassen sich bis zu drei Ranks (ein Double-Rank und ein Single-Rank) mit 1T ansprechen, bei mehr muss man entweder die Command Rate verlängern oder die Taktfrequenz absenken.

Wichtige Parameter zum Zeitverhalten des Speichers sind:

RAS-to-CAS-Delay – Zeilenoperationen

Column Address Select bzw. Column Address Strobe, dieses Steuersignal liegt während einer gültigen Spaltenadresse an. Der Speicherbaustein legt diese Adresse in einem Zwischenspeicher ab.

Synchrone DRAMs (SDRAM, DDR-SDRAM) besitzen ebenfalls die Steuereingänge RAS und CAS, jedoch haben sie hier ihre unmittelbare Funktion verloren. Stattdessen werden bei synchronen DRAMs die Kombination aller Steuersignale (CKE, RAS, CAS, WE, CS) bei steigender Clock-Flanke ausgewertet, um zu entscheiden, ob und in welcher Form die Signale auf den Adressleitungen interpretiert werden müssen.

Dem Vorteil der Einsparung von externen Adressleitungen steht ein scheinbarer Nachteil in Form einer verzögerten Verfügbarkeit der Spaltenadresse gegenüber. Die Spaltenadresse wird jedoch erst nach der Dekodierung der Zeilenadresse, der Aktivierung einer Wortleitung und dem Bewerten des Bitleitungssignals benötigt. Dieser interne Vorgang benötigt jedoch ca. 15 ns, so dass sich die verzögert erhaltene Spaltenadresse nicht negativ auswirkt.

RAS Active Time tRAS

Der Parameter tRAS (RAS pulse width, Active Command Period, Bank Active Time) beschreibt die Zeit, die nach der Aktivierung einer Zeile (bzw. einer Zeile in einer Bank) verstrichen sein muss, bevor ein Kommando zum Deaktivieren der Zeile (Precharge, Schließen der Bank) gesendet werden darf. Der Parameter ist dadurch gegeben, dass die Verstärkung der Bitleitungsspannung und das Rückschreiben der Information in die Zelle vollständig abgeschlossen sein muss, bevor die Wortleitung deaktiviert werden darf.

RAS Precharge Time tRP

Der Parameter tRP (Row Precharge Time) beschreibt die Zeit, die nach einem Precharge-Kommando mindestens verstrichen sein muss, bevor ein erneutes Kommando zur Aktivierung einer Zeile in der gleichen Bank gesendet werden darf. Diese Zeit ist durch die Bedingung definiert, dass alle Spannungen im Zellenfeld (Wortleitungsspannung, Versorgungsspannung der Leseverstärker) abgeschaltet sind und die Spannungen aller Leitungen (insbesondere die der Bitleitungen) wieder auf ihrem Ausgangsniveau angekommen sind.

RAS Cycle Time tRC

Dies beschreibt die Zeit zwischen zwei Gesamt-Zyklen, vom Precharge bis zum Precharge.

Fehlererkennung (ECC)

Speichermodule können je nach Bestückung verwendet werden

- ohne Fehlererkennung

- mit Fehlererkennung (Parität)

- mit Fehlerkorrektur (ECC)

Für die einfache Fehlererkennung mittels Paritätsbit wird je 8 bit Wortbreite ein weiteres Bit benötigt, die Module sind folglich 9 bit (einfaches SIMM), 36 bit (PS/2-SIMM) oder 72 bit breit (übliche DIMMs) organisiert. Ein einzelnes DIMM bietet damit auch genügend Bit-Breite für die Nutzung der Fehlerkorrektur (siehe unten), während hierzu mehrere gleichartige PS/2-Module parallel geschaltet werden müssen.

Die Fehlerkorrektur muss außerdem von der Hauptplatine (Chipsatz und BIOS) unterstützt werden, die zusätzlichen Bits auf den Modulen schaffen nur die Möglichkeit zur Ablage der benötigten Information.

Zur Erkennung von Hauptspeicherfehlern gibt es mehrere Verfahren. Eines dieser Verfahren stammt vom US-Mathematiker Richard Hamming: Der Error Correction Code (ECC) ist eine Art Hashwert über die 64 Bits jeder Speicherzeile. Diese redundanten Informationen werden vom Speichercontroller berechnet und in acht weiteren Bits abgelegt (bei 32-bit-Speicherzeilen sind es sieben weitere Bits), weshalb ECC-Speicher 72 Bits pro Zeile hat. Das Verfahren selbst heißt Error Checking and Correcting.

ECC kann alle 1-bit-Fehler korrigieren und alle 2-bit-Fehler sowie manche Mehr-bit-Fehler erkennen. ECC-Speicher kommt in Desktop-PCs kaum zum Einsatz.

Weitere Techniken zur Fehlererkennung sind unter den Namen Chipkill, Active Memory, Memory Resiliency oder Memory RAID bekannt.

Die Hauptursache von Speicherfehlern ist nicht ionisierende Strahlung (wie früher vermutet), sondern eher Probleme einzelner Speicherzellen (zum Beispiel durch Alterung oder Fertigungsprobleme).[4][5]

Vergleichstabelle

Besitzt ein Hauptprozessor (Grafikprozessor, FPGA o. ä.) zwei, drei, vier oder mehr Speicherinterfaces, kann sich im Idealfall die Datenübertragungsgeschwindigkeit verdoppeln, verdrei-, vervier- oder entsprechend der Anzahl der Speicherinterfaces vervielfachen. AMDs Prozessor Athlon 64 FX zum Beispiel besitzt zwei Speicher-Interfaces, der Athlon 64 im Sockel 754 verfügt dagegen über nur ein Speicher-Interface.

| Bustakt | Busbreite | Bezeichnung | Datenrate | |

|---|---|---|---|---|

| DDR- SDRAM | 133 MHz | 64 bit | PC2100 | 2,133 GB/s |

| 166 MHz | 64 bit | PC2700 | 2,667 GB/s | |

| 200 MHz | 64 bit | PC3200 | 3,200 GB/s | |

| DDR- SDRAM2 | 200 MHz | 64 bit | PC2-3200 | 3,200 GB/s |

| 266 MHz | 64 bit | PC2-4200 | 4,267 GB/s | |

| 333 MHz | 64 bit | PC2-5300 | 5,333 GB/s | |

| 400 MHz | 64 bit | PC2-6400 | 6,400 GB/s | |

| DDR- SDRAM3 | 400 MHz | 64 bit | PC3-6400 | 6,400 GB/s |

| 533 MHz | 64 bit | PC3-8500 | 8,533 GB/s | |

| 666 MHz | 64 bit | PC3-10600 | 10,667 GB/s | |

| 800 MHz | 64 bit | PC3-12800 | 12,800 GB/s | |

| DDR- SDRAM4 | 800 MHz | 64 bit | PC4-12800 | 12,800 GB/s |

| 933 MHz | 64 bit | PC4-14900 | 14,933 GB/s | |

| 1066 MHz | 64 bit | PC4-17100 | 17,067 GB/s | |

| 1200 MHz | 64 bit | PC4-19200 | 19,200 GB/s | |

| 1333 MHz | 64 bit | PC4-21300 | 21,333 GB/s | |

| 1600 MHz | 64 bit | PC4-25600 | 25,600 GB/s | |

| RDRAM | 400 MHz | 16 bit | PC800 | 1,600 GB/s |

| 533 MHz | 16 bit | PC1066 | 2,133 GB/s | |

| 600 MHz | 16 bit | PC1200 | 2,400 GB/s | |

| 800 MHz | 16 bit | PC1600 | 3,200 GB/s | |

| 1066 MHz | 16 bit | PC2100 | 4,267 GB/s |

Die Angabe der Datenrate dient nur der Klassifizierung und entspricht daher nicht der Nutzdatenrate.

Siehe auch

Literatur

- Horst Völz: Speicher als Grundlage für Alles. Shaker Verlag, Düren 2019, ISBN 978-3-8440-6964-8.

Einzelnachweise

- ↑ Memory ranks and Intel E7320 / E7520 chipset based servers ( vom 31. März 2010 im Internet Archive) (PDF; 278 kB). Kingston Technology memory ranking technical brief, April 2005.

- ↑ Corsair DDR2 FAQ ( des vom 11. Oktober 2006 im Internet Archive) Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis. (PDF; 80 kB), Februar 2004. What’s the difference between a rank and a bank?

- ↑ https://www.micron.com/products/dram/ddr4-sdram

- ↑ heise.de Hauptspeicherfehler sehr viel häufiger als bisher angenommen (2009)

- ↑ cs.toronto.edu (PDF; 284 kB) DRAM Errors in the Wild: A Large-Scale Field Study, Mai 2009.

Weblinks

- Speicher-Links und -FAQ, heise.de

- Arbeitsspeicher/Hauptspeicher – RAM, CPU+Mainboard-FAQ, dch-faq.de

- Speichermodul – Arbeitsspeicher-Glossary und -FAQ, CompuRAM, München

Auf dieser Seite verwendete Medien

SDR-DIMM-Ram Modul M1:1

Micro-DIMM-Ram Modul M1:1

RIMM-Ram Modul M1:1

S0-Simm-Ram Modul M1:1

Zeichnung eines SIMM-RAMs M1:1

DDR-DIMM-Ram Modul M1:1

S0-RIMM-Ram Modul M1:1

Autor/Urheber: PantheraLeo1359531, Lizenz: CC BY 4.0

Ansicht des RAM-Moduls "Micron MTC40F204681RC48BA1R". Das Modul ist ein RAM-Modul mit DDR5-SDRAM-Technologie (DDR5-4800), ECC und RDIMM mit 1,1V und CL40. Auf der Leiterplatte sind 64 GiB (ca. 65536 MiB) zuhause. Dieser RAM wird meist in Servern und Workstations eingesetzt. Es gibt auch ein Modell mit 96 GiB. Eingescannt mit Epson-Scanner. Besonders auffällig ist die großzügige Bestückung von Speicherchips, die bei 64 GiB auch nötig sind.