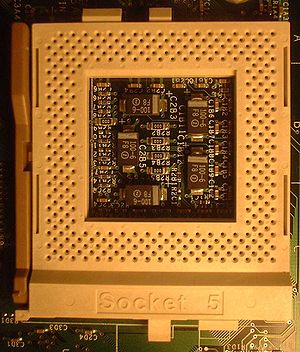

Sockel 5

| Sockel 5 | |

|---|---|

| |

| Spezifikationen | |

| Einführung | Zur CeBit 1994 |

| Bauart | SPGA-ZIF |

| Kontakte | 320 |

| Busprotokoll | eigenes, Intel hat nie eine Bezeichnung eingeführt |

| Bustakt | 50 MHz, 60 MHz, 66 MHz |

| Betriebsspannung | variable Spannung von 3,1 bis 3,6 V |

| Prozessoren | Intel Pentium (75–120 MHz) Intel Pentium Overdrive (125–166 MHz) Intel Pentium MMX Overdrive (125–200 MHz) AMD K5 (PR75–PR200) IDT WinChip (180–200 MHz) IDT WinChip-2 (200–240 MHz) IDT WinChip-2a (233 MHz) und kompatible |

Der Sockel 5 ist ein Prozessorsockel und der Nachfolger von Sockel 4. Er ist gedacht für frühe Pentium-Prozessoren vom Typ P54C. Spätere Versionen des P54C und der Nachfolger P55C nutzen hingegen den in seiner Urform zum Sockel 5 weitgehend kompatiblen Sockel 7, welcher auch alle für den Sockel 5 vorgesehenen CPUs aufnehmen kann.

Das Busprotokoll des Sockel 5 gleicht in weiten Teilen dem des Sockel 4. Die hinzugekommenen Anschlüsse betreffen ausschließlich das vereinfachte Dual-Processing, den nun in die CPU integrierten Advanced Programmable Interrupt Controller – APIC genannt – und die Stromsparmodi des neuen Pentium-Typs. Weggefallen sind hingegen ein paar unwichtigere oder in der Praxis kaum genutzte Anschlüsse des ersten Pentium-Typs P5. Darüber hinaus hat Intel aus Gründen der Leistungsaufnahme die Spannungsversorgung beim Sockel 5 auf etwa 3,3 Volt – abhängig von der verwendeten CPU – gesenkt. Dementsprechend haben sich auch die logischen Signalpegel verändert, das Signal-Timing entspricht aber weiterhin weitgehend dem des Sockel 4.

Ein neuer Pin, der BF-Pin, gestattet beim Sockel 5 darüber hinaus das Einstellen verschiedener Taktverhältnisse zwischen Prozessorbus und Prozessorkern. Viele Sockel-5-Hauptplatinen erlauben das Setzen dieses Pins über einen Jumper, BF- oder BF0-Jumper genannt. Die ersten P54C-Pentium (Pentium-Varianten mit 75 MHz, 90 MHz und 100 MHz) laufen mit einem Bustakt-zu-Kerntakt-Verhältnis von 2:3, spätere (Varianten mit 120 MHz oder 133 MHz) mit einem Verhältnis von 1:2. Mit dem BF0-Jumper kann zwischen diesen beiden Verhältnissen gewählt werden.

Der Sockel 5 wurde ab dem Pentium mit 133 MHz durch den in seiner Urform praktisch funktionsgleichen Sockel 7 abgelöst, der statt eines BF-Pins zwei, später sogar drei besaß. So ist je nach eingesetzter CPU das Einstellen von bis zu vier bzw. acht unterschiedlichen Bustakt-zu-Kerntakt-Verhältnissen möglich.

Unverständlich ist, dass Intel zwischen Sockel 5 und Sockel 7 zunächst überhaupt unterschieden hat. Funktional bestand anfangs zwischen beiden ein weitaus geringerer Unterschied als zwischen dem frühen und dem späten, für den Pentium MMX vorgesehenen Sockel-7-Typ.

Der Sockel 5 nutzt wie der Sockel 7 ZIF-Sockel ein Staggered-Pin-Grid-Array-Layout (SPGA), d. h. die Kontaktreihen sind versetzt angeordnet, um eine höhere Packungsdichte zu erreichen.