Physical Address Extension

Physical Address Extension (englisch für Erweiterung (der) physischen Adressierung), kurz PAE, ist eine technische Erweiterung auf dem Gebiet der Rechnerarchitektur. Mit PAE kann im 32-Bit-Modus eines x86-kompatiblen Prozessors (CPUs) mehr physischer Arbeitsspeicher adressiert werden als die 4 GiB, die über ein 32-Bit-Adressregister erreichbar sind.[1] Der für einen Prozess nutzbare Arbeitsspeicher bleibt bei einem linearen Speichermodell („flat memory“) aber auf 4 GiB begrenzt. Das Verfahren wird bei Intel ab dem Pentium Pro und bei AMD ab dem Athlon sowie bei Prozessoren der 32-Bit-x86-Architektur IA-32 anderer Hersteller eingesetzt. Spezielle Erweiterungen in der Paging-Einheit des Prozessors sorgen dafür, dass längere physische Adressen generiert werden können.

Begriff

Selten wird der Begriff auch mit Bindestrich verwendet („Physical-Address Extension“), das ist theoretisch die korrekte Schreibweise gemäß englischer Grammatik und wird vor allem seitens AMD so verwendet. Vorherrschend ist jedoch die Schreibweise ohne Bindestrich.

Unterstützung durch Hardware

| Prozessor | Adress- leitungen | theoretisch adressierbarer physikalischer Speicher |

|---|---|---|

| i386 bis Pentium | 32 | 4 GiB (kein PAE) |

| Pentium Pro (P6) bis Core 2 | 36 | 64 GiB |

| Xeon | 38 | 256 GiB |

| Athlon 64 (K8) | 40 | 1.024 GiB = 1 TiB |

| AMD-K10-Architektur | 48 | 262.144 GiB = 256 TiB |

| theoretisches Limit von PAE | 52 | 4.194.304 GiB = 4.096 TiB |

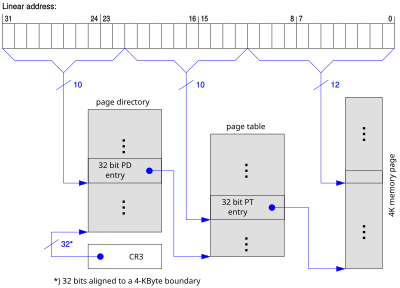

x86-Prozessoren, die PAE unterstützen, haben eine erweiterte Paging-Einheit. Die Paging-Einheit (in der Grafik dargestellt) wandelt die lineare Adresse in die physische Adresse um. Um PAE zu aktivieren, muss das Betriebssystem das Bit 5 im Steuerregister CR4 setzen.[2]

Bei aktiviertem PAE verwalten die Page-Directory- und Page-Table-Tabellen (PD und PT) der Paging-Einheit Adress-Einträge mit einer Breite von 64 Bit statt 32 Bit (bei jedem Adress-Eintrag werden einige Bits zur Verwaltung benutzt, sind also keine Adresse im engeren Sinn).

| Bits: | 63 | 62 … 52 | 51 … 32 | |||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Inhalt: | NX | reserved | Bit 51 … 32 der Basisadresse | |||||||||||||||||||||||||||||

| Bits: | 31 … 12 | 11 … 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||||||||||||||||||||

| Inhalt: | Bit 31 … 12 der Basisadresse | AVL | ig | 0 | ig | A | PCD | PWT | U/S | R/W | P | |||||||||||||||||||||

Damit die Größe der Tabellen unverändert bei 4 KiB bleibt, verwalten das PD und die PT nur noch jeweils die Hälfte der Einträge (512 statt 1024). Um den Rückgang auf ein Viertel der möglichen Adresseinträge auszugleichen, ist der PD-PT-Kombination eine weitere, sogenannte Page-Directory-Pointer-Tabelle vorgeschaltet, die 4 PDs statt eines PDs ansprechen kann.

Die angegebenen theoretisch adressierbaren Speichermengen des physikalischen Speichers sind Maximalwerte. In der Regel ist trotzdem nur weniger Speicher nutzbar, da einige Adressbereiche für Einblendungen von Hardwarespeicher genutzt werden. In Microsoft Windows kann in den Computereigenschaften gesehen werden, wie viel Speicher dem Betriebssystem tatsächlich zur Verfügung steht. Nur im Idealfall entspricht diese Zahl dem installierten Arbeitsspeicher. Dabei muss auch beachtet werden, dass viele Windows-Versionen willkürliche Speicherobergrenzen haben, die auch von der Edition abhängen. Alle Client-Versionen von 32-Bit-Ausgaben sind z. B. auf 4 GiB beschränkt.

Unterstützung durch Betriebssysteme

Zur Nutzung von PAE muss dieses auch vom Betriebssystem unterstützt werden. PAE führt allerdings zu längeren Zugriffszeiten durch die virtuelle Speicherverwaltung, das Paging und für 32-Bit PCI-Zugriffe, die bei einer Begrenzung des Arbeitsspeichers auf 4 GiB nicht erforderlich wären.

Auf den meisten Rechnern ist PAE dennoch aktiviert, da nur mit eingeschalteter PAE das No-Execute-Bit genutzt werden kann. Dieses soll verhindern, dass in Datenbereichen Schadsoftware eingeschleust werden kann, die zu einem Virenbefall des Rechners führen. Dazu werden entsprechende Datenbereiche als „nicht ausführbar“ markiert. Wenn ein Sprung an eine Adresse in einem solchen Bereich erfolgt, kommt es zu einer Schutzverletzung und das entsprechende Programm wird angehalten. Da einige nicht sauber programmierte Software dadurch nicht mehr funktionieren würde, ist es in Microsoft Windows standardmäßig nur für betriebssystemeigene Prozesse eingeschaltet. Dadurch wird die ursprünglich angedachte höhere Sicherheit nur für OS-eigene Funktionen erreicht.

BSD-Familie

FreeBSD unterstützt PAE in der 4.x Serie ab 4.9, in der 5.x Serie ab 5.1 und in allen 6.x Versionen und allen späteren Versionen. Die PAE-Konfigurationsoption wird im Kernel benötigt. Ladbare Kernelmodule können nur in einen Kernel mit aktiviertem PAE geladen werden, wenn die Module mit aktiviertem PAE erstellt worden sind. Nicht alle Treiber unterstützen mehr als 4 GiB Arbeitsspeicher, in einem System mit aktiviertem PAE laufen solche Treiber nicht richtig. NetBSD sowie OpenBSD (bisher nur in -current) unterstützen PAE ebenfalls. Alle adressieren den gesamten 64-GiB-Adressraum.

Haiku

Haiku unterstützt PAE ab der Version Haiku R1 Alpha 3.[3]

Linux

Der Linux-Kernel enthält ab der Version 2.3.23 vom 22. Oktober 1999 die volle PAE-Unterstützung. Seit 2009 ist PAE bei vielen Linux-Distributionen per Voreinstellung enthalten, weil PAE für das NX-Bit benötigt wird.

Ein Patch von Mitte 2014 führte unter Linux den Kernel-Kommandozeilenparameter forcepae ein,[4] der auf einigen Pentium-M- und Celeron-M-Prozessoren PAE aktiviert. Frühen Modellen mit Dothan-Kern und allen Modellen mit Banias-Kern fehlt die Angabe von PAE in deren CPUID, obwohl die Funktion im Prozessor vorhanden ist. Mitte 2014 endete die Unterstützung von Microsoft für Windows XP, gleichzeitig änderten viele Linux-Distributionen die Mindestanforderungen ihrer 32-Bit-Varianten auf „i686+pae“,[5] obwohl es teilweise Community-Kernel für ältere Systeme (i486 oder i586, ohne PAE) gibt. Mit „forcepae“ ließen sich viele Standard-Distributionen auch auf Systemen von rund 2004/2005 mit Pentium M bzw. Celeron M ohne Austausch des Kernels nutzen, beispielsweise auf ThinkPads oder Toughbooks.[6]

macOS

macOS für Intel-Macs unterstützt PAE und das NX-Bit ab der ersten Intel-Version, Mac OS X Tiger (Version 10.4.4) vom Januar 2006, auf allen von Apple unterstützten x86-Prozessoren. Modelle der Mac-Pro-Serie werden seit 2008 mit bis zu 64 GiB RAM ausgeliefert.

Solaris

Solaris unterstützt PAE ab Version 7.

Windows

PAE wird von Microsoft Windows ab Version 2000 (Professional und höher) und XP (alle Varianten) unterstützt und muss hierbei zumeist durch eine Bootoption aktiviert werden. Allerdings ist dabei bei den 32-bit Desktop-Versionen auch mit aktiviertem PAE der maximal nutzbare Hauptspeicher auf 4 GB beschränkt. Dies wird zum einen damit erklärt, dass es wohl Teil der Vermarktungspolitik von Microsoft sei.[7] Microsoft dagegen begründet diese Einschränkung damit, dass einige der verwendeten Gerätetreiber beim Zugriff auf Speicherbereiche jenseits der 4 GB Probleme bereiten würden.[8]

Anwendungen können erweiterten Speicher je nach Hardware und Betriebssystem möglicherweise über Address Windowing Extension (AWE) nutzen. Je nach Windows-Version müssen eventuell zusätzliche Service Packs eingespielt werden, es existieren auch einige inoffizielle Patches für 32-Bit Vista und Windows 7, die die Nutzung bis 64 GB ermöglichen.[9][10]

Andere CPU-Plattformen

Auf ARM gibt es ab ARMv7 die sogenannte Large Physical Address Extension, die einen ähnlichen Ansatz verfolgt und es ermöglicht, im 32-Bit-Modus bis zu 240 Bytes physischen Speicher anzusprechen.[11]

Siehe auch

Einzelnachweise

- ↑ https://www.intel.com/content/www/us/en/content-details/782158/intel-64-and-ia-32-architectures-software-developer-s-manual-combined-volumes-1-2a-2b-2c-2d-3a-3b-3c-3d-and-4.html?wapkw=intel%2064%20and%20ia-32%20architectures%20software%20developer%27s%20manual&docid=782161%7CIntel® 64 and IA-32 Architectures Soft- ware Developer’s Manual, Volume 3A Kapitel 4.4 Seite 3114

- ↑ support.amd.com (PDF)

- ↑ Release Notes: Haiku R1 Alpha 3 (18. Juni 2011)

- ↑ Chris Bainbridge: [tip:x86/cpu] x86, cpu: Add forcepae parameter for booting PAE kernels on PAE-disabled Pentium M. In: Linux-Kernel-Mailingliste LKML.org. 20. Februar 2014, abgerufen am 2. Januar 2024 (englisch).

- ↑ [PATCH] x86: set Pentium M as PAE capable. (Mailingliste) In: lore.kernel.org. 2014, abgerufen am 2. Januar 2024 (englisch, gesamte Diskussion).

- ↑ David Wolski: Xubuntu und Lubuntu mit uralten CPUs nutzen. In: PC-Welt. 22. Oktober 2014, abgerufen am 2. Januar 2024.

- ↑ geoffchappell.com

- ↑ Mark Russinovich: Pushing the Limits of Windows: Physical Memory. 21. Juli 2008, archiviert vom am 28. April 2010; abgerufen am 4. September 2013.

- ↑ 32位Vista/Win 7 4GB大内存补丁 ReadyFor4GB. (deutsch: 32-Bit Vista/Win 7 – 4 GB großer Speicher-Patch ReadyFor4GB). 26. April 2009, abgerufen am 17. März 2011 (chinesisch).

- ↑ Unawave: Windows 7 32-bit with full 4 GB or 8 GB RAM support. Abgerufen am 11. Juli 2010.

- ↑ https://developer.arm.com/documentation/ddi0406/latest/DDI0406C_d_armv7ar_arm.pdf Kapitel B.16

Auf dieser Seite verwendete Medien

Autor/Urheber: RokerHRO, Lizenz: CC BY-SA 3.0

Schematische Darstellung der Umsetzung von linearen in physische Adressen bei x86-kompatiblen CPUs im 32-Bit Protected Mode. Seitengröße: 4 KiByte, kein PAE.

Autor/Urheber: RokerHRO, Lizenz: CC BY-SA 3.0

Schematische Darstellung der Umsetzung von linearen in physische Adressen bei x86-kompatiblen CPUs im 32-Bit Protected Mode. Seitengröße: 4 KiByte, mit PAE.

Autor/Urheber: RokerHRO, Lizenz: CC BY-SA 3.0

Schematische Darstellung der Umsetzung von linearen in physische Adressen bei x86-kompatiblen CPUs im 32-Bit Protected Mode. Seitengröße: 4 MiByte, kein PAE.

Autor/Urheber: RokerHRO, Lizenz: CC BY-SA 3.0

Schematische Darstellung der Umsetzung von linearen in physische Adressen bei x86-kompatiblen CPUs im 32-Bit Protected Mode. Seitengröße: 2 MiByte, mit PAE.