Leistungs-MOSFET

Ein Leistungs-MOSFET (englisch power MOSFET, power metal oxide semiconductor field-effect transistor) ist eine spezialisierte Version eines Metall-Oxid-Halbleiter-Feldeffekttransistors (MOSFET), der für das Leiten und Sperren von großen elektrischen Strömen und Spannungen optimiert ist (bis mehrere hundert Ampere und bis ca. 1000 Volt, bei einem Bauteilvolumen von etwa einem Kubikzentimeter).

Leistungs-MOSFETs unterscheiden sich von bipolaren Leistungstransistoren sowohl in der Funktionsweise als auch in der Effizienz. Einige Vorteile von Leistungs-MOSFETs sind die schnelle Schaltzeit, kein zweiter Durchbruch und stabile Verstärkungs- und Antwortzeiten. Ab einer Strombelastbarkeit von etwa 1 A wird ein MOSFET den Leistungs-MOSFETs zugeordnet.

Geschichte

Ein Antrieb zur Entwicklung der Power-MOSFETs waren die Schwächen der bis dahin dominierenden bipolaren Leistungstransistoren (englisch bipolar power junction transistor, BJT). Bipolare Leistungstransistoren benötigen z. B. hohe Steuerströme bis ca. 1/5 des Laststromes, während Leistungs-MOSFETs im ein- bzw. ausgeschalteten Zustand prinzipiell keinen Steuerstrom benötigen.

Physikalische Funktionsweise

Leistungs-MOSFETs arbeiten nach dem gleichen physikalischen Prinzip wie die in integrierten Schaltungen verwendeten MOSFETs, sie unterscheiden sich jedoch durch andere geometrische Formen und Dimensionen. Die hohe Leistungsdichte wird durch eine raster- oder wabenartige Halbleiterstruktur erreicht, die einer Parallelschaltung von tausenden einzelnen MOSFETs entspricht.

Auch der Aufbau des Leistungs-MOSFET entspricht dem des MOSFET – allerdings ergeben sich zahlreiche Besonderheiten. Im Gegensatz zum Signaltransistor der Nachrichtentechnik ist die Anordnung von Source und Drain vertikal. In der Halbleiterstruktur von Gate, Drain und Source entstehen in einem MOSFET zahlreiche parasitäre Elemente, wie z. B. Widerstände, Kapazitäten und Dioden. In der Leistungselektronik muss diesen parasitären Elementen besondere Beachtung geschenkt werden. Die Kapazitäten müssen bei jedem Schaltvorgang umgeladen werden, was besonders bei hohen Schaltfrequenzen zu erheblichen Schaltverlusten führt. Die meisten MOSFETs enthalten eine parasitäre Diode. Das liegt daran, dass die Bulk-Zone aus Optimierungsgründen intern mit dem Sourceanschluss verbunden ist. Diese Diode ist im Normalbetrieb in Sperrrichtung geschaltet. Ist sie im Datenblatt des Bauteils spezifiziert, kann sie schaltungstechnisch ausgenutzt werden, wie eine zu Drain und Source parallel geschaltete Diode. Je nach Anforderung müssen dabei noch weitere Effekte berücksichtigt werden.

Es gibt hauptsächlich drei Typen von Leistungs-MOSFETs – die DMOS-, UMOS- und die VMOS-Struktur. Sie besitzen eine große Drain-Drift-Region, welche das Bauteil gegen Durchbruch bei hohen Sperrspannungen schützt.

DMOS-Feldeffektransistor

MOSFETs dieses Strukturaufbaus werden durch Doppelimplantation der Kanalstruktur hergestellt und als DMOSFET (engl. double-diffused metal-oxide semiconductor field effect transistor) bezeichnet.[1][2] Beim NMOS-Typ befindet sich der Kanal im schmalen p-Gebiet unterhalb der Gate-Elektrode, siehe Bild.

Für Leistungs-MOSFETs sind Transistoren mit großem Verstärkungsfaktor und kleinem Durchlasswiderstand erforderlich. Mit DMOSFETs lässt sich das durch eine große Kanalweite und Parallelschaltung erreichen und zwar in kompakter Weise auf Chip-Ebene. Es existieren primär quadratische (z. B. SIPMOS) und hexagonale (z. B. HEXFET™ von International Rectifier, jetzt Infineon Technologies) Strukturen. Die Source-Elektrode befindet sich zuoberst als großflächige Schicht, darunter liegt vergraben die Gate-Elektrode.

Eine Besonderheit des DMOSFET ist u. a., dass er im Rückwärtsbetrieb (VDS < 0) keine Sperrfähigkeit aufweist. Die Inversdiode des p-n-Übergangs zwischen Basis und Kollektor des parasitären npn-Bipolartransistors befindet sich dann in Flusspolung. Das wird beim Schalten induktiver Lasten ausgenutzt, hier kann die Inversdiode als Freilaufdiode wirken und so durch Kurzschluss die beim Abschalten der induktiven Last entstehende hohe Spannung kurzschließen. Jedoch muss beachtet werden, dass die Inversdioden bei MOSFETs für höhere Sperrspannungen deutlich höhere Sperrverzugsladungen und Schaltverluste aufweisen als herkömmliche schnelle Dioden. Auch wenn besondere Techniken (z. B. FREDFET) verwendet werden, um das Verhalten der Inversdiode zu verbessern, sind diese Dioden immer noch um einen Faktor von ca. 3 schlechter als separate schnelle Dioden. Die Verwendung der Inversdiode bei MOSFETs mit Sperrspannungen größer 200 V in Anwendungen zum Schalten induktiver Last mit hoher Frequenz ist daher oft nicht möglich.

UMOS-Feldeffektransistor

Der UMOS-Feldeffekttransistor (von engl. U-shaped notch MOS field-effect transistor, UMOS-FET, auch U-MOSFET) ist eine vertikaler Leistungs-MOSFET-Struktur, bei der die Gate-Elektrode in einem im Silizium geätzten Graben ausgeführt wird, von dessen U-Form sich der Name ableitet. Die Nutzung des Grabens als Gate-Elektrode führt zu einem vertikalen Kanal.

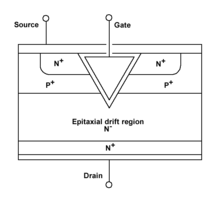

VMOS-Feldeffektransistor

Der VMOS-Feldeffekttransistor (von engl. v-groved MOS field-effect transistor) ist ein nicht-planarer Feldeffekttransistor, bei dem mithilfe eines V-förmigen Gatebereichs die Kanallänge reduziert und die Kanalweite erhöht wird. Der V-förmige Graben für den Gatebereich wird häufig durch anisotropes Ätzen von Silizium hergestellt. Vorgestellt wurde das Konzept Mitte der 1970er Jahre von T. J. Rodgers.[3] Es gibt sowohl Varianten mit lateralem als auch mit vertikalem Stromfluss, wobei die vertikale Variante häufiger zu finden ist. Durch die bessere Nutzung der Chipfläche ermöglichen VMOS-FETs eine höhere Stromdichte und eignen sich daher vor allem für den Einsatz als (diskreter) Leistungs-MOSFET. Zudem zeichnen sie sich durch eine hohe Eingangsimpedanz aus.

Anwendungen

Leistungs-MOSFETs werden häufig in Verstärkerschaltungen, als stromlos steuerbarer Schalter und als schneller Schalter für Pulsweitenmodulation eingesetzt, z. B. in Wechselrichtern, Schaltnetzteilen, DC/DC-Wandlern oder Motorsteuerungen.

Bei Schaltanwendungen ist die schnelle Strom-Anstiegszeit von MOSFETs von Vorteil. Damit lassen sich die Umschaltverluste senken.

Induktive Lasten erzeugen beim Schaltvorgang große Spannungsspitzen, gegen die der Leistungs-MOSFET, wie auch andere Halbleiterschalter, geschützt sein muss. Dieser Schutz kann jedoch bei MOSFETs im Bauteil selbst erreicht werden, indem der Avalancheeffekt beim Durchbruch kontrolliert abläuft, ohne die Bauelementstrukturen partiell zu überhitzen. Oft ist jedoch dennoch eine zusätzliche externe Beschaltung (Snubber) notwendig.

Auch bei Leistungs-MOSFETs fällt Verlustleistung an, was für die Kühlung genau betrachtet werden muss. Das Parallelschalten von MOSFETs ist zumindest in Schaltanwendungen unproblematischer als mit bipolaren Transistoren. Der Temperaturkoeffizient von MOSFETS ist für kleine Stromwerte stark positiv, hat im Verlauf einen Nullpunkt und ist für große Werte negativ. In Schaltanwendungen wird UGS möglichst schnell in den Bereich oberhalb des Null-Temperaturkoeffizienten geschaltet. In diesem Bereich wird die Stromverteilung der Einzeltransistoren also durch den Temperaturkoeffizienten ausgeglichen. Bei Linearschaltungen trifft das keineswegs zu, denn hier wird UGS auch im Bereich des positiven Temperaturkoeffizienten betrieben. Gerade die MOSFET-Typen mit sehr niedrigem RDS haben den Nullpunkt des Temperaturkoeffizienten weiter nach oben verlagert, sind also für Parallelschaltungen in Linearschaltungen weniger geeignet.[4]

Kenngrößen

Wie bei bipolaren Leistungstransistoren, ist der sichere Arbeitsbereich (engl. safe operating area, SOA) bei Leistungs-MOSFETs durch drei Kenngrößen bestimmt:

- Maximaler Drain-Strom

- Durchbruchspannung (auch ) und die dadurch vorgegebene maximale Sperrspannung

- Maximale Verlustleistung

Weitere wichtige Kenngrößen:

- Minimaler Durchgangswiderstand

- Maximal zulässige Energie beim Avalanche-Durchbruch

- Ladungsmenge Qg, die für das Ein- und Ausschalten notwendig ist (Ansteuerverluste)

- max. Spannungsänderungsgeschwindigkeit

Anders als Bipolartransistoren vertragen MOSFETs sehr hohe Werte für die Spannungsänderungsgeschwindigkeit, sie müssen nicht durch Snubber-Glieder dagegen geschützt werden. Der sogenannte zweite Durchbruch (Zerstörung durch kleine Ströme bei Spannungen unterhalb der Sperrspannung) tritt bei MOSFETs kleiner Leistung üblicherweise nicht auf, sofern die Verlustleistung nicht überschritten wird. Bei Leistungs-MOSFETs hingegen kann es im Sättigungs- oder Linearbetrieb (der Drainstrom wird maßgeblich durch die Gatespannung gesteuert) durch lokale Überhitzungen im Halbleiter zur Beschädigung kommen. Ursache ist der negative Temperaturkoeffizient der Schwellspannung, nahe der man sich in diesem Betriebszustand aufhält. Hier ist die sogenannte SOA-Kennlinie (Safe Operating Area) zu beachten, die der Hersteller angibt.[5]

Weiterentwicklung

In den meisten Fällen wird der Drain-Source-Durchlasswiderstand (englisch on-state resistance) bei einer vorgegebenen Durchbruchspannung als wesentliches Merkmal von Leistungs-MOSFETs betrachtet. Grundsätzlich gilt bei gegebener Chipfläche: je größer die maximale Sperrspannung des MOSFET, desto größer ist sein Durchlasswiderstand. Bei herkömmlichem Schichtaufbau kommt es bei einer Verdopplung der Spannungsfestigkeit zu einer Verfünffachung des . Ebenso wächst die Chipfläche mit einem Exponenten von 2,4 bis 2,6. Dieser Zusammenhang wird im Englischen als Silicon-Limit bezeichnet.[6]

Bei der Reduzierung des Durchlasswiderstands bei hohen Spannungen, über rund 200 V, erzielten die Halbleiterhersteller in den späten 1990er Jahren Fortschritte, welche zur breiten Anwendung von Leistungs-MOSFETs führten. Dabei werden in die wegen der höheren Spannungsfestigkeit normalerweise dicker gestalteten n−-Epitaxieschicht zusätzliche p-Zonen eingebracht, welche im Sperrzustand den Verlauf der elektrischen Feldstärke modulieren und lokale Durchbrüche im Silicium verhindern. Damit kann die n−-Epitaxieschicht dünner werden, was auch bei hohen Spannungen einen geringeren Bahnwiderstand zur Folge hat.

Der Drain-Source-Durchlasswiderstand variiert mit der Durchbruchspannung:

Ein üblicher Wert ist im Jahr 2017 ein von 30 mΩ bei einer Sperrspannung von 250 V im Gehäuse TO-247. Bei maximalen Sperrspannungen um 50 V sind Werte um einige wenige Milliohm üblich.

Neben der allgemeinen Verbesserung der Robustheit gegen Strom- und Spannungsspitzen und der Verringerung des Durchlasswiderstands werden zunehmend weitere Funktionen in das Bauteil integriert. Diese Bauteile werden häufig als „Smart Power Devices“ bezeichnet und enthalten neben Schutzschaltungen (Eingangsschutz, Schutz gegen thermische Überlastung, Strombegrenzung, Fehlersignalgenerierung) z. B. level shifting (Schalten der positiven Lastleitung mit einem massebezogenen Signal, sogenannte high side switches) oder sogar vollständige PWM-Controller.

Bauformen

Übliche Gehäusebauformen von Leistungs-MOSFETs sind für durchkontaktierte Platinen beispielsweise TO-264, TO-247 und TO-220, bei oberflächenmontierbaren (SMD) Bauelementen DPak, D²Pak und SO-8. Darüber hinaus gibt es noch Gehäuse mit Schraubanschlüssen für Leitungen oder Stromschienen. Dazu zählen das SOT-227 „Isotop“ mit vier Schraubanschlüssen. Der Source-Anschluss wird dabei doppelt herausgeführt, um ein genaueres Referenzpotential zur Gate-Ansteuerung zur Verfügung zu haben.

Literatur

- Arendt Wintrich, Ulrich Nicolai, Werner Tursky, Tobias Reimann: Applikationshandbuch Leistungshalbleiter. ISLE Verlag, 2010, ISBN 978-3-938843-56-7 (semikron.com [PDF]).

Weblinks

- Vrej Barkhordarian: Power MOSFET Basics. (PDF; 83 kB; englisch) International Rectifier

Einzelnachweise

- ↑ Patent US5055895: Double-Diffused Metal-Oxide Semiconductor Field Effect Transistor Device. Veröffentlicht am 8. Oktober 1991, Anmelder: Matsushuta Electric Works LTD, Erfinder: Sigeo Akiyama, Masahiko Suzumura, Takeshi Nobe.

- ↑ Thomas Tille: Mikroelektronik: Halbleiterbauelemente und deren Anwendung in elektronischen Schaltungen. Springer, Berlin 2005, ISBN 978-3-540-20422-0

- ↑ T.J. Rodgers, J.D. Meindl: VMOS: high speed TTL compatible MOS logic. In: Solid-State Circuits, IEEE Journal of. Band 9, Nr. 5, 1974, S. 239–250, doi:10.1109/JSSC.1974.1050509.

- ↑ Peter H. Wilson: MOSFET thermal instabiliy, Application Note, V1.0, May 2005. (PDF) Infineon Technologies, 1. Mai 2005, abgerufen am 16. Oktober 2020 (englisch).

- ↑ International Rectifier Application Note AN-1155

- ↑ Joachim Specovius: Grundkurs Leistungselektronik. 4. Auflage. Vieweg + Teubner, 2010, ISBN 978-3-8348-1307-7.

Auf dieser Seite verwendete Medien

Autor/Urheber: Mister rf, Lizenz: CC BY-SA 4.0

IRF130 internal view: Power MOSFET, N Channel, 100 V, 14 A, 0.18 ohm; 75 W: TO-3 packaging; Manufacturer: International Rectifier

Autor/Urheber: Cyril BUTTAY, Lizenz: CC BY-SA 3.0

This is the 3-D view of a power MOSFET (cross section). The gate layout is meshed, with square-shaped cells

Autor/Urheber: Die Autorenschaft wurde nicht in einer maschinell lesbaren Form angegeben. Es wird CyrilB~commonswiki als Autor angenommen (basierend auf den Rechteinhaber-Angaben)., Lizenz: CC BY-SA 3.0

Cyril BUTTAY --

Two MOSFET in D2PAK package. These are 30-A, 120-V-rated each.Autor/Urheber:

Der ursprünglich hochladende Benutzer war Cepheiden in der Wikipedia auf Deutsch

Later version(s) were uploaded by Henristosch at de.wikipedia.

Schematischer Aufbau eines n-Kanal-de:DMOSFETs

This is a diagram of the cross-section of VMOSFET.