Flip-Chip-Montage

Die Flip-Chip-Montage (dt. „Wende-Montage“), auch bekannt als controlled collapse chip connection (C4), ist ein Verfahren der Aufbau- und Verbindungstechnik (AVT) zur Kontaktierung ungehäuster Halbleiter-Chips (englisch bare die) mittels Bumps, d. h. Kontaktierhügeln.

Bei der Flip-Chip-Montage wird der Chip direkt, ohne weitere Anschlussdrähte, mit der aktiven Kontaktierungsseite nach unten montiert, d. h. zum Substrat / Schaltungsträger hin; daher auch der Name Flip-Chip (engl. to flip, umdrehen). Dies führt zu besonders geringen Abmessungen des Gehäuses und kurzen Leiterlängen.

Bei sehr komplexen Schaltkreisen bietet die Flip-Chip-Montage oft die einzige sinnvolle Verbindungsmöglichkeit, weil zum Teil mehrere tausend Kontakte realisiert werden müssen. So kann die gesamte Fläche des Die zur Kontaktierung genutzt werden, im Gegensatz zum Drahtbonden, wo dies nicht oder nur begrenzt möglich ist, weil sich die Drähte kreuzen und wahrscheinlich miteinander in Berührung kommen würden. Weiterhin werden beim Drahtbonden die Verbindungen nacheinander hergestellt, während bei der Flip-Chip-Bondtechnik alle Kontakte gleichzeitig angeschlossen werden, was Zeit spart.

Um die Chips zu bonden, wird neben Löten und leitfähigem Kleben (s. ICA und ACA) auch Pressschweißen (thermode bonding) als Fügeverfahren angewendet.

Weitere Package-Bauformen sind unter Chipgehäuse gelistet.

C4-Technologie

C4 steht für die Zusammenfassung der Anfangsbuchstaben der Begriffe „controlled collapsed chip connection“ (= CCCC = C4).

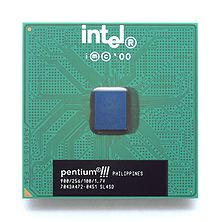

Die C4-Flip-Chip-Technologie wurde 1964 von IBM eingeführt und erfuhr seitdem mehrere Modifikationen. Diese Technik wird z. B. bei der Herstellung komplexer Mikroprozessoren verwendet. Man kann sich die Herstellung wie folgt vorstellen: Der Wafer wird ganzflächig mit einem Metall beschichtet, z. B. durch Sputtern. Nun erfolgt das Aufbringen einer Lackmaske mit definierten Öffnungen. Anschließend wird galvanisch das Lot abgeschieden. Die Lackmaske wird entfernt. Dadurch entstehen zylindrische Lotkörper, wie von der Lackmaske vorgegeben. Diese Lotzylinder bilden die Kontaktpunkte, welche die Verbindung zu den Schaltungsstrukturen in den tieferen Schichten des Wafers bzw. jedes einzelnen Dies herstellen. Mit einem selektiven Ätzverfahren wird die übrige, nicht vom abgeschiedenen Lot abgedeckte Metallschicht entfernt. Die Lotzylinder werden anschließend zu kleinen Kugeln (bumps) aufgeschmolzen (Reflow). Dann werden die Wafer zu Silizium-Chips vereinzelt. Die Chips werden mit einem Flussmittel benetzt und der Aufbau erwärmt, so dass das Lot aufschmilzt und eine elektrische Verbindung zwischen den Kontaktflächen des Chips und den Kontakten des Substrates (Gehäuse, Package) herstellt (Reflow-Löten).

Eine weitere Methode, um einen Wafer mit den Bumps zu versehen, ist der Schablonendruck. Der Wafer wird, nachdem er mittels Galvanik eine lötbare Oberfläche an den Pads erhalten hat, in einem Schablonendrucker mit Lotpaste bedruckt. Danach wird der Wafer auch hier einem Reflowprozess unterzogen, die Lotpaste schmilzt um und es entstehen Bumps. Anschließend kann der Wafer gereinigt werden, um Flussmittelreste zu entfernen. Es folgt die Vereinzelung der Chips und die Verarbeitung nach dem Benetzen mit Flussmittel im SMD-Fertigungsprozess.

Nach dem Löten auf das Substrat (Gehäuse, „Package“) oder die Leiterplatte benötigt der Aufbau einen sogenannten Underfill (ein elastischer, temperaturbeständiger Kunststoff), damit die unterschiedlichen thermischen Ausdehnungskoeffizienten von Chip und Substrat den Aufbau nicht zerstören.

Nach dem Underfill-Prozess sieht der Flip Chip wie folgt aus:

Kleben mit nicht leitfähigem Klebstoff (NCA)

Die Technologie wird häufig als NCA-Verfahren (non-conductive adhesive, dt. nicht leitfähiger Klebstoff) bezeichnet. Hier sind die Kontakte des Chips in der Regel mit so genannten Stud-Bumps versehen, die aus Golddraht bestehen. Die Stud-Bumps werden im Drahtbondverfahren (Ball-Wedge-Verfahren) aufgebracht und dann direkt über dem Ball abgerissen. Teilweise werden die Bumps dann noch mittels eines speziellen Werkzeugs abgeflacht und auf eine gleichmäßige Höhe gebracht (Coining).

Auf das Substrat wird ein nicht leitfähiger Klebstoff (meist auf Epoxid-Basis) aufgebracht und der Chip hinein gepresst (gebondet). Der Druck beim Bestücken muss ausreichend hoch sein, dass die Stud-Bumps die Kleberschicht sicher durchstoßen um eine elektrische Verbindung herstellen zu können. Anschließend wird der Kleber unter erhöhter Temperatur ausgehärtet, wobei das Werkzeug mit dem Chip unter konstantem Druck stehen sollte. Wichtig für eine sichere Verbindung ist, dass der Klebstoff beim Trocknen schrumpft, so dass die Bumps auf die Kontaktflächen des Substrats gezogen werden und ein elektrischer Kontakt entsteht.

Die NCA-Technologie ist von allen Flip-Chip-Montageverfahren am besten für kleine Serien geeignet, da das Bumping der Halbleiter-Chips auch nach der Separation des Wafers noch möglich ist. Auch der Bestückungsprozess ist gut für niedrige Stückzahlen geeignet. Die erzielbaren Kontakt-Abstände sind recht klein, das bedeutet, dass eine hohe Integration möglich ist. Durch den flächigen Verlauf des Klebstoffes unter dem Chip entfällt die Notwendigkeit eines separaten Underfill-Prozesses.

Das Chip-Bonden unter Druck führt zu einer relativ hohen Taktzeit, da das Bestückwerkzeug eine gewisse Abkühlzeit benötigt, um den Härteprozess beim nächsten Teil nicht zu früh einzuleiten. Für Großserien ist das Stud-Bumping zudem kein idealer Bumping-Prozess, da das serielle Ball-Bonden wesentlich mehr Zeit benötigt als flächige Auftragsverfahren wie Siebdruck oder Sputtern.

Kleben mit isotrop leitfähigem Klebstoff (ICA)

Dieses Verfahren wird mit ICA (isotropic-conductive adhesive, dt. isotrop leitfähiger Klebstoff) bezeichnet. Auf die Kontakte des Substrates wird ein isotrop leitfähiger Klebstoff aufgebracht. Dann wird der Chip mit seinen Kontakten (mit Bumps) auf die Klebepunkte gesetzt. Der Klebstoff wird thermisch oder mittels UV-Strahlung gehärtet und stellt so eine mechanische und elektrische Verbindung her. Da der Klebstoff nicht vollflächig aufgebracht wird, ist nach dem Aushärten in der Regel noch ein Underfill notwendig. Die Bumps werden bei diesem Verfahren meist auf Wafer-Ebene aufgebracht, z. B. durch Sputtern oder Aufdampfen von Nickel. Stud-Bumps sind möglich, werden aber eher selten eingesetzt.

Der Prozess muss im Gegensatz zum NCA- oder ACA-Verfahren nicht seriell ablaufen, das heißt, es können viele Chips in einem Durchgang ausgehärtet werden. Das führt zu einer verminderten Taktzeit. Die zum Aushärten benötigten Temperaturen sind in der Regel niedriger als beim Löten, die thermische Belastung des Bauteils ist folglich geringer.

Diese Art der Kontaktierung ist auf wenige und relativ große Kontakte beschränkt, da sich der Klebstoff nicht beliebig fein auftragen lässt und außerdem beim Aufsetzen des Chips verläuft. Das Verfahren bietet kaum Vorteile gegenüber dem Löten von Flip-Chips, macht aber einen zusätzlichen Prozess notwendig, während das Löten in der Aufbau- und Verbindungstechnik (AVT) als Standardprozess integriert ist. Aus diesen Gründen wird dieses Verfahren eher selten angewendet.

Kleben mit anisotrop leitfähigem Klebstoff (ACA)

Das Verfahren wird als ACA (anisotropic-conductive adhesive, dt. anisotrop leitfähiger Klebstoff) bezeichnet. Anisotrop leitfähiger Klebstoff besteht aus einem Klebstoff, der schwach mit kleinen leitfähigen Partikeln gleicher Größe gefüllt ist, z. B. mit Gold beschichtete Polymerkugeln. Der Klebstoff wird vollflächig über die Kontakte des Substrates aufgebracht. Durch den geringen Füllfaktor der leitfähigen Partikel stehen diese nach dem Auftrag nicht in Verbindung, so dass sich keine leitfähige Schicht ergibt, die die Kontakte kurzschließen würde. Beim Aufsetzen des Chips wird der Klebstoff durch den mechanischen Druck verdrängt und die leitfähigen Partikel verdichtet, bis diese zwischen Bumps und Substrat-Pads eingeklemmt werden und so eine leitfähige Verbindung herstellen. Um eine sichere Verbindung zu gewährleisten, wird der Druck während des Aushärteprozesses aufrechterhalten. Die Bumps werden wie beim ICA-Verfahren meist direkt auf dem Wafer erzeugt.

Ein Vorteil ist eine flächige Verklebung des Chips, so dass ein zusätzlicher Underfill-Prozess nicht mehr notwendig ist. Weiterhin sind die erzielbaren Kontaktabstände (Pitch) sehr klein, deutlich geringer als beim ICA-Verfahren. Der beim Bestücken notwendige Druck ist deutlich geringer als beim NCA-Verfahren, was eine geringere mechanische Belastung zur Folge hat.

Ein Nachteil ist, wie beim NCA-Verfahren, dass der Chip während des Härtens des Klebstoffs auf das Substrat gedrückt werden muss (Thermokompression), damit der elektrische Kontakt erhalten bleibt, was sich negativ auf den Durchsatz auswirkt. Außerdem ist ACA-Kleber aufgrund seines komplexen Aufbaus und einer geringen Anzahl von Herstellern relativ teuer.

Weblinks

- Hintergrund zum Flip Chip Prozess ( vom 15. März 2016 im Internet Archive) – englisch

- Wissenschaftliche Studie zur Flip-Chip-Montage auf MID - (PDF; 8,3 MB)

- Forschungsinstitut im Bereich der Flip-Chip-Technologie

Auf dieser Seite verwendete Medien

Autor/Urheber: Binder-Elektronik-Wissen, Lizenz: CC BY-SA 3.0

Prinzipbild der NCA-Technologie

Autor/Urheber: Binder-Elektronik-Wissen, Lizenz: CC BY-SA 3.0

Prinzipbild zur Flip-Chip-Technologie ACA

Physikalisch bedingte diverse Ausdehungskoeffizenten zwischen FR4, Aluoxid und Silizium

Verarbeiteten Chip

Autor/Urheber: Binder-Elektronik-Wissen, Lizenz: CC BY-SA 3.0

Prinzipbild zur Flip-Chip-Technologie ICA

Autor/Urheber: Konstantin Lanzet, Lizenz: CC BY-SA 3.0

CPU Intel Pentium III Coppermine.