Erasable Programmable Logic Device

Ein Erasable Programmable Logic Device (EPLD, engl., dt. etwa „löschbares programmierbares Logikbauelement“) ist ein bereits als historisch zu bezeichnender, durch UV-Licht löschbarer programmierbarer Logikbaustein, der in der Floating-Gate-Technologie aufgebaut ist. Im Vergleich zu PAL-Bausteinen ist die Anzahl der Gatter, die programmiert werden können, um einiges höher.

Bei der Programmierung des EPLD wird auf dem isolierten Floating-Gate Ladung gespeichert, die mit UV-Licht wieder gelöscht werden kann, da diese Strahlung die Ladungen wieder entfernt. Ein geladenes Floating-Gate stellt dabei eine Unterbrechung dar. Ein EPLD ist aus einer Und-Gatter-Eingangsmatrix aufgebaut, die programmiert werden kann, sowie aus einer Oder-Ausgangsmatrix, welche bereits fest verdrahtet auf dem Chip ist.

Die EPLDs gibt es seit etwa 1984. Sie werden heute kaum noch eingesetzt und sind praktisch vollständig durch CPLDs oder FPGAs ersetzt worden.

Literatur

K. Weigl: Anwendungsprogrammierbare Logik mit EPLD. In: Design & Elektronik. Teil 1: Nr. 18, 1986 und Teil 2: Nr. 19 1986.

Weblinks

Auf dieser Seite verwendete Medien

Altera EP1200 programmable logic device was introduced in 1985. The device used UV erasable technology and could hold the equivalent of 1200 logic gates. It came in a 40 pin 600 mil DIP package. Intel was a second source.

Image made by placing the IC on an Epson Perfection V500 Photo scanner.(c) I, NobbiP, CC BY-SA 3.0

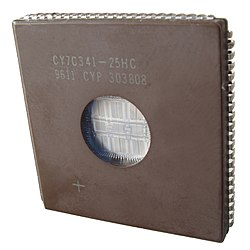

Ceramic LCC Package, 84 Pins, Cypress UV erasable, 1996