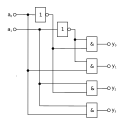

1-aus-n-Decoder

Bei monolithischen integrierten Schaltkreisen werden statt der Und-Gatter häufig NAND-Gatter verwendet.

Ein 1-aus-n-Decoder ist eine Schaltung mit n Ausgängen und log2(n) Eingängen. In der Praxis muss aber die Anzahl der Eingänge auf die nächste ganze Zahl aufgerundet werden, wenn log2(n) keine ganze Zahl ist. Der jeweils adressierte Ausgang geht dann auf High, wenn die Dualzahl A am Eingang der Nummer J des betreffenden Ausgangs yJ entspricht. Die anderen Ausgänge werden dann nicht angesteuert und bleiben auf Low.

| Wert | Eingang | Ausgang | ||||||

|---|---|---|---|---|---|---|---|---|

| A=J | a1 | a0 | y3 | y2 | y1 | y0 | ||

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | ||

| 1 | 0 | 1 | 0 | 0 | 1 | 0 | ||

| 2 | 1 | 0 | 0 | 1 | 0 | 0 | ||

| 3 | 1 | 1 | 1 | 0 | 0 | 0 | ||

Diese Schaltungsfunktion wird direkt in handelsüblichen Bauelementen realisiert. Gebräuchliche IC-Bausteine sind der TTL-Baustein 74LS42 und der CMOS-Baustein 4028 mit jeweils zehn Ausgängen.

Diese Logikfunktion wird darüber hinaus in komplexen integrierten Logikbauelementen verwendet. Beispielsweise wird diese Funktion als Zeilendecoder und Spaltendecoder zur Adressierung der Zeilen und Spalten in Speicherbauelementen (RAM, ROM, EEPROM, …) verwendet. Darüber hinaus kann diese Logikfunktion auch in einer programmierbaren logischen Schaltung (PLD) oder einem FPGA-Bauelement oder einem ASIC-Bauelement realisiert werden.

Siehe auch

Auf dieser Seite verwendete Medien

Autor/Urheber: — MovGP0, Lizenz: CC BY-SA 2.0 de

Schaltung eines 1-aus-n-Decoders