X86 Paging PAE 4K

Relevante Bilder

Relevante Artikel

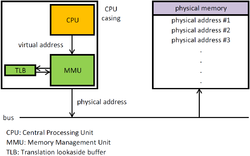

Physical Address ExtensionPhysical Address Extension, kurz PAE, ist eine technische Erweiterung auf dem Gebiet der Rechnerarchitektur. Mit PAE kann im 32-Bit-Modus eines x86-kompatiblen Prozessors (CPUs) mehr physischer Arbeitsspeicher adressiert werden als die 4 GiB, die über ein 32-Bit-Adressregister erreichbar sind. Der für einen Prozess nutzbare Arbeitsspeicher bleibt bei einem linearen Speichermodell aber auf 4 GiB begrenzt. Das Verfahren wird bei Intel ab dem Pentium Pro und bei AMD ab dem Athlon sowie bei Prozessoren der 32-Bit-x86-Architektur IA-32 anderer Hersteller eingesetzt. Spezielle Erweiterungen in der Paging-Einheit des Prozessors sorgen dafür, dass längere physische Adressen generiert werden können. .. weiterlesen

PagingAls Paging bezeichnet man die Methode der Speicherverwaltung per Seitenadressierung durch Betriebssysteme. Nur selten wird die deutsche Bezeichnung Kachelverwaltung verwendet. .. weiterlesen